Abstract

Standard approaches to quantum error correction for fault-tolerant quantum computing are based on encoding a single logical qubit into many physical ones, resulting in asymptotically zero encoding rates and therefore huge resource overheads. To overcome this issue, high-rate quantum codes, such as quantum low-density parity-check codes, have been studied over the past decade. In this case, however, it is difficult to perform logical gates in parallel while maintaining low overheads. Here, we propose concatenated high-rate small-size quantum error-detecting codes as a family of high-rate quantum codes. Their simple structure allows for a geometrical interpretation using hypercubes corresponding to logical qubits. We thus call them many-hypercube codes. They can realize both high rates, e.g., 30% (64 logical qubits are encoded into 216 physical ones), and parallelizability of logical gates. Developing dedicated decoder and encoders, we achieve high error thresholds even in a circuit-level noise model. Thus, the many-hypercube codes will pave the way to high-performance fault-tolerant quantum computing.

Proposed quantum error-correcting codes allow for high encoding rates, high performance, and a beautiful geometrical code structure.

INTRODUCTION

Quantum computers have been expected to outperform current classical computers by harnessing quantum superposition states. However, the quantum superpositions are notoriously fragile. The so-called decoherence leads to many errors in quantum computers, spoiling quantum computation. A standard approach to this issue is quantum error correction. Careful use of quantum error-correcting codes can protect quantum computation from errors, which is called fault-tolerant quantum computation (1–3). A standard quantum error-correcting code for this purpose is the surface code (4–10), which requires only a two-dimensional qubit array with nearest-neighbor interactions and therefore is suitable for, e.g., superconducting-circuit implementations (11–13). However, the surface code uses many physical qubits to protect a single logical qubit. More precisely, the number of physical qubits to encode a single logical qubit is the square of the code distance, where the code distance characterizes the code size and we can, in principle, correct arbitrary physical-qubit errors if their number is less than half the code distance. This means that the encoding rate defined as the ratio of the number of logical qubits to that of physical qubits vanishes rapidly as the code size becomes larger, resulting in large resource overheads (14–16).

In contrast, quantum low-density parity-check (qLDPC) codes (17) are known for their ability to achieve constant encoding rates and therefore have been studied over the past decade to mitigate the above overhead issue (18, 19). Various kinds of qLDPC codes have been proposed (20–28), high-performance decoders for them have also been developed (29–35), and their physical implementations have recently been proposed (36–40). However, they have relatively complex structures, making it difficult to implement logical gate operations in a fault-tolerant manner. A few methods for this purpose have been proposed (18, 39–43), but parallel execution of logical gates maintaining the advantage of the qLDPC codes, i.e., low overheads, is still challenging.

Recently, a completely different approach to the constant encoding rate has been proposed (44), which is based on a more conventional approach called code concatenation. Concatenation means recursive encoding with multiple codes. By increasing the encoding rates for higher concatenation levels, this proposal achieved a finite rate for the infinite code size. This also allows for parallel execution of logical gates with constant overheads, unlike qLDPC codes. In other words, this proposal offers time-efficient, constant-space-overhead fault-tolerant quantum computation. However, this approach based on quantum Hamming codes has two issues. First, the encoding rate is not very high, converging to 1/36. Second, the decoding of the concatenated codes is based on hard-decision decoding, which is known to be suboptimal and has relatively low performance.

In this work, we propose another family of high-rate concatenated quantum codes. The characteristic feature of our proposal is the use of quantum error-detecting codes (2), which have distance 2 and therefore can detect an error but cannot correct it. By concatenating the error-detecting codes, we can increase the code distance and thus obtain error-correcting codes. The advantage of the quantum error-detecting codes is their simple structure. Harnessing this advantage, Knill proposed concatenated quantum error-detecting codes called the C4/C6 scheme and achieved the realization of the error threshold exceeding 1% in a circuit-level noise model (45). [Recently, the concatenation of the C4/C6 scheme and the concatenated quantum Hamming codes mentioned above has been proposed to improve the performance of the latter (46), but this still has the above-mentioned two issues, that is, the rate becomes rather lower and the decoding is still based on hard-decision decoding.] However, the C4/C6 scheme is based on a single-logical-qubit encoding, like the surface code, and therefore its encoding rate approaches zero rapidly as the code size increases. Unlike the C4/C6 scheme, the proposed concatenated codes have high encoding rates. In this work, we focus on the ⟦6,4,2⟧ code, which encodes four qubits into six qubits and has distance 2. (The reason for choosing this code is its relatively high rate and small size. The use of other codes, such as ⟦4,2,2⟧ and ⟦8,6,2⟧, is also interesting but left for future work.) By concatenating it (L − 1) times, we obtain the ⟦N(L), K(L), D(L)⟧ = ⟦6L,4L,2L⟧ code, which we refer to as the ⟦6L,4L,2L⟧ level-L many-hypercube code or simply the level-L many-hypercube code for the reason explained later. Although it is not a constant-rate code, that is, its rate, K(L)/N(L) = (4/6)L, approaches zero as L becomes larger, the rate is remarkably high for small L, e.g., 30% (20%) at level 3 (4) with distance 8 (16), which is higher than not only the surface code but also well-studied qLDPC codes (36–40). Thus, the many-hypercube codes will be promising as a near-term target. Note that the number of logical qubits is not limited to K(L) = 4L. Using M code blocks encoded with the level-L many-hypercube code as fault-tolerant quantum registers (44), we can use MK(L) logical qubits for fault-tolerant quantum computing.

We developed a high-performance decoder dedicated to the many-hypercube codes based on level-by-level minimum distance decoding. (Our proposed decoding method will also be useful for other concatenated codes, such as the above concatenated quantum Hamming codes.) Using this decoder, we achieved a threshold of 5.6% for bit-flip errors, which is comparable to the surface code (10.9%) (47) and a 4%-rate qLDPC (hypergraph product) code (7.5%) (33). We also propose fault-tolerant zero-state encoders for the many-hypercube codes. Using them, we achieved a threshold of 0.9% for a logical controlled-NOT (CNOT) gate in a circuit-level noise model. Last, we explain how to perform logical gates for the many-hypercube codes in parallel.

RESULTS

Many-hypercube codes

We start with the definition of the ⟦6,4,2⟧ code. The ⟦6,4,2⟧ code is one of the simplest stabilizer codes (3) and has only two stabilizer generators (check operators): SZ = Z1Z2Z3Z4Z5Z6 and SX = X1X2X3X4X5X6, which can detect an X (bit-flip) error and a Z (phase-flip) error, respectively, in its six-qubit code block (see Materials and Methods for the definitions of elementary gates). Its four logical qubits are defined by the following logical Z and X operators

| (1) |

| (2) |

| (3) |

| (4) |

Other definitions are possible (2), but we use this because of the geometrical interpretation of the code structure using hypercubes explained below. By the definition, the logical all-zero state of the ⟦6,4,2⟧ code is the six-qubit Greenberger-Horne-Zeilinger (GHZ) state

| (5) |

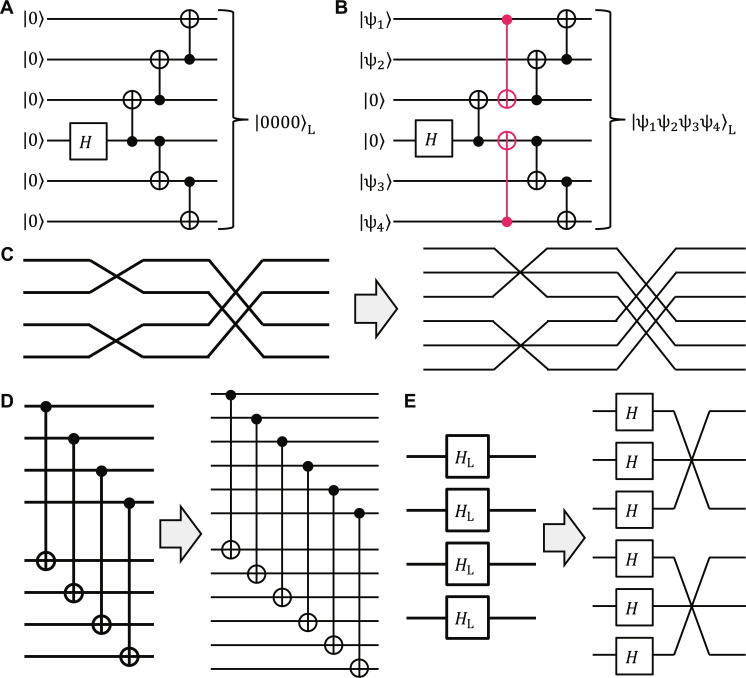

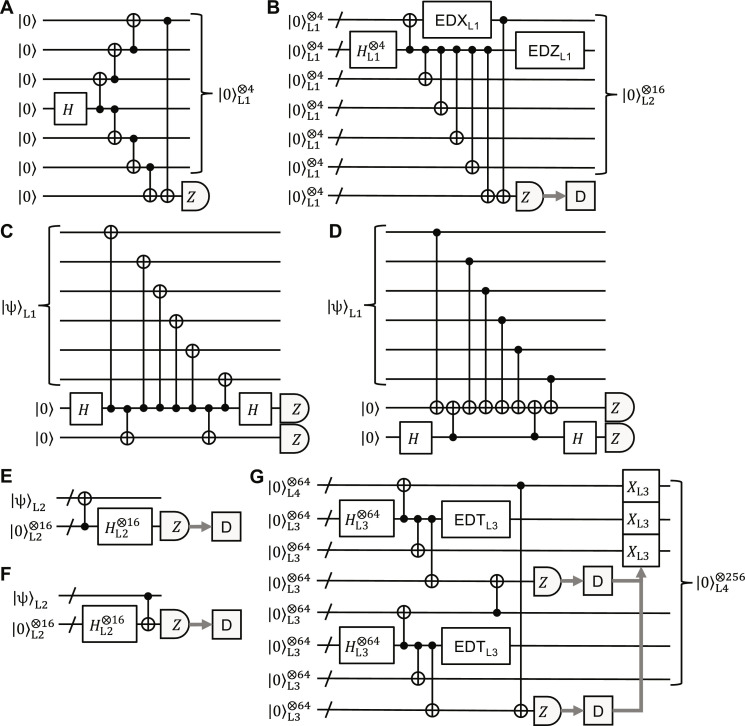

Therefore, the zero-state encoder of the ⟦6,4,2⟧ code is given by, e.g., the quantum circuit shown in Fig. 1A. This can be generalized to an arbitrary-state encoder by adding two CNOT gates, as shown in Fig. 1B. The logical SWAP gates between the logical qubits 1 and 2, 3 and 4, and (1,2) and (3,4) can be performed by physical SWAP gates between the physical qubits 1 and 3, 4 and 6, and (1,2,3) and (4,5,6), respectively, as shown in Fig. 1C. We can also easily find that transversal logical CNOT and Hadamard gates can be performed by transversal physical CNOT and Hadamard (and SWAP) gates, respectively, as shown in Fig. 1 (D and E).

Fig. 1. Encoders and logical gates of the ⟦6, 4, 2⟧ code.

(A) Zero-state encoder. (B) Arbitrary-state encoder. In (B), additional two CNOT gates are highlighted in red. (C) Logical SWAP gates. (D) Transversal logical CNOT gates. (E) Transversal logical Hadamard gates. In (C) to (E), the left and right sides correspond to logical and physical ones, respectively.

Using the ⟦6,4,2⟧ code recursively, e.g., the level-3 many-hypercube code is defined as follows. Each of the physical and encoded qubits is labeled by three integers (corresponding to the three levels) and denoted by Q with subscripts of the integers. The corresponding operators are also labeled similarly. The four level-1 qubits are encoded into the corresponding six physical qubits {Qi,j,k ∣ i = 1, …,6} with the ⟦6,4,2⟧ code (j,k = 1, …,6), where the two stabilizers and encoded Z and X operators are defined as follows

| (6) |

| (7) |

| (8) |

| (9) |

| (10) |

| (11) |

Similarly, the four level-2 qubits are encoded into the corresponding six level-1 qubits (i′ = 1, …,4, k = 1, …,6) and the four level-3 qubits are encoded into the corresponding six level-2 qubits (i′,j′ = 1, …,4). In this case, we use the 64 level-3 encoded qubits as logical qubits in a fault-tolerant quantum register for quantum computing. In general, the level-L many-hypercube code is defined similarly.

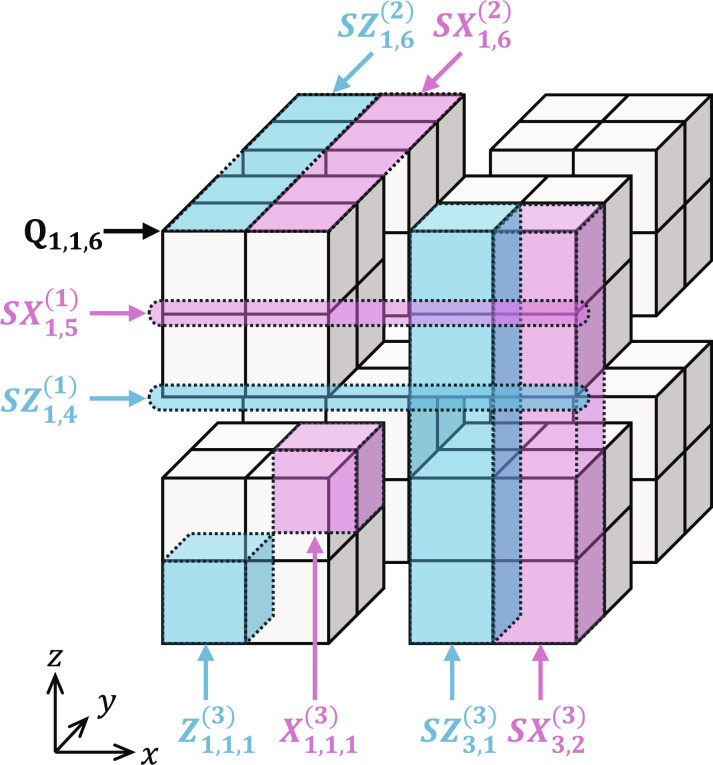

The above code structure can be visualized as shown in Fig. 2 by placing the physical qubit Qi,j,k at the point with the coordinates (x, y, z) = (i, j, k) in a three-dimensional space, where the logical Z and X operators correspond to cubes. For example

| (12) |

| (13) |

are highlighted in light blue and pink, respectively, in Fig. 2. Also, the level-l stabilizers correspond to l-dimensional objects on the cubes, e.g., as follows

| (14) |

| (15) |

| (16) |

| (17) |

| (18) |

| (19) |

which are also highlighted in light blue (SZ) and pink (SX) in Fig. 2.

Fig. 2. Visualization of the structure of the level-3 many-hypercube code.

The vertices correspond to physical qubits. Examples of logical Z and X operators and stabilizers in Eqs. 12 to 19 are highlighted in light blue (Z) and pink (X).

In general, in a similar visualization, the logical Z and X operators of the level-L many-hypercube code correspond to L-dimensional hypercubes in an L-dimensional space and also its level-l stabilizers correspond to l-dimensional objects on the hypercubes, where the number of the hypercubes is equal to that of the logical qubits. This is the reason for the name of the proposed code. [The “many” is used to distinguish it from a conventional hypercube code (48), which is the ⟦2D, D,2⟧ code defined on a single D-dimensional hypercube.]

The number of the vertices of each L-dimensional hypercube, 2L, is equal to the code distance. That is, the size of the many-hypercube codes is increased by increasing not the edge length but the dimension while keeping the edge length. In contrast, the logical operators and stabilizers of topological codes, such as the surface code (4–10) and the color code (49–52), correspond to the edges and faces, respectively, and their code sizes are increased by increasing the edge length. Unlike the topological codes, the many-hypercube codes require interactions beyond nearest-neighbor ones. This is experimentally challenging, but recent experimental advances in ion-trap (53–59) and neutral-atom (60–63) systems are encouraging. Hypercube connectivity has already been realized experimentally (63).

Decoders

In this work, we investigated three decoding methods for the many-hypercube codes. The first one is Knill’s method proposed for the C4/C6 scheme (45), which we refer to as hard-decision decoding. The second one is soft-decision decoding based on a posteriori probability calculation (64, 65). The original soft-decision decoding is based on block-MAP (maximum a posteriori probability) decoding, which cannot be applied directly to high-rate codes such as the many-hypercube codes because then we must calculate a posteriori probabilities for an exponentially large number of codewords. We thus modified it to symbol-MAP decoding applicable to high-rate codes. The third one is our proposed method based on level-by-level minimum distance decoding, where we keep only minimum-distance codewords from measurement outcomes as candidates at each level from level 1 to the logical level. See Materials and Methods and the Supplementary Materials for the details of the three methods.

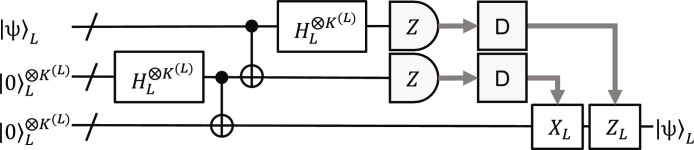

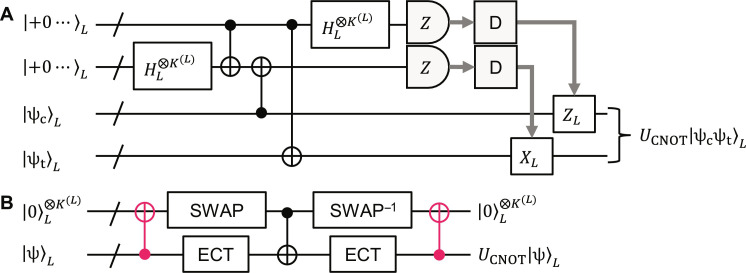

In the following, we assume that error correction is done by error-correcting teleportation (ECT) (45, 65, 66). This is quantum teleportation with logical qubits, where the classical feed-forward information is determined by decoding physical-qubit measurement outcomes, as shown in Fig. 3. Thus, the decoding is the task to estimate the measurement outcomes of logical qubits from those of physical ones in the logical Bell measurements. Note that, in ECT, we obtain all the syndrome information at once; no need to repeatedly measure them one by one, unlike the Shor method (1, 18) used for the surface code and qLDPC codes. Assuming that the two ancilla registers used for the quantum teleportation are reliable sufficiently, the errors in ECT come mainly from the decoding error. Also note that all the errors to be decoded are included in the physical-qubit measurement errors in the Bell measurement, and therefore in the case of ECT, decoders designed for independent physical-qubit errors are directly applicable to circuit-level noise models. In this work, we also assume that all the measurements are done in the Z basis {|0⟩, |1⟩}, resulting in bit-value outcomes.

Fig. 3. Error-correcting teleportation.

The input logical-qubit state encoded with the level-L many-hypercube code, |ψ⟩L, on the left side is teleported with two logical all-zero states to the right side. The gray bold arrows show the flow of the classical information. The “D” boxes are the decoders, which decode the physical-qubit measurement outcomes and provide logical-qubit ones. If a logical-qubit outcome is 1, then the corresponding logical Z or X operator is performed on the corresponding logical qubit. The transversal logical CNOT and Hadamard gates are performed by transversal physical CNOT and Hadamard gates, as shown in Fig. 1 (D and E), respectively.

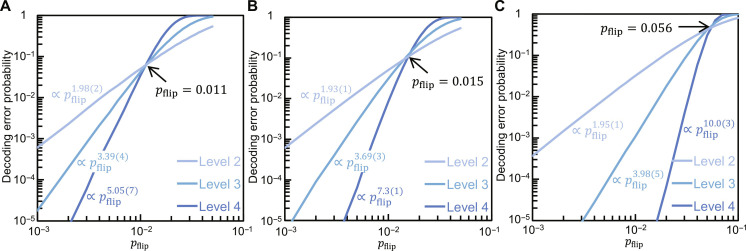

We numerically evaluated the performance of the three decoding methods using a bit-flip error model (see Materials and Methods for details). In this work, stabilizer quantum-circuit simulations in our numerical study were done using a Python package called Stim (67). The decoding error probabilities estimated by the simulations are shown in Fig. 4. First, the exponents of the power-function fits for the hard-decision decoding are smaller than half the code distance, as in the case of the C4/C6 scheme (65), which shows its suboptimality. On the other hand, the exponents for the other two are near to or even exceed half the distance, showing their high performance. Second, the error thresholds are estimated at 1.1, 1.5, and 5.6%, respectively, and only our minimum distance decoding is comparable to the surface code (10.9%) (47) and a well-studied qLDPC (4%-rate hypergraph product) code (7.5%) (33). Thus, our proposed decoding method achieves the highest performance among the three methods.

Fig. 4. Performance of three decoders of the many-hypercube codes for bit-flip errors.

(A) Hard-decision decoder. (B) Symbol-MAP decoder. (C) Level-by-level minimum distance decoder. The exponents are estimated by fitting a power function to the linear parts of the log-log plots. The thresholds indicated by arrows are defined by the intersection points of the level-3 and level-4 curves. See Materials and Methods for the details of the three decoding methods and the simulation.

Fault-tolerant zero-state encoders

Hereafter, we consider a circuit-level noise model with error rate pcirc. In this work, we assume the following noise model. Each of the physical-qubit zero-state preparation and Z-basis measurement is accompanied by a bit flip with probability pcirc, and each two-qubit (CNOT) gate is followed by 1 of 15 two-qubit Pauli errors with equal probability pcirc/15 (8). On the other hand, we assume no single-qubit-gate and memory errors for simplicity. This model is relevant for ion-trap (53–59) and neutral-atom (60–63) systems. (Even for these systems, it is eventually desirable to consider the effect of the neglected errors, but it requires thorough optimization of time overheads and therefore is left for future work.)

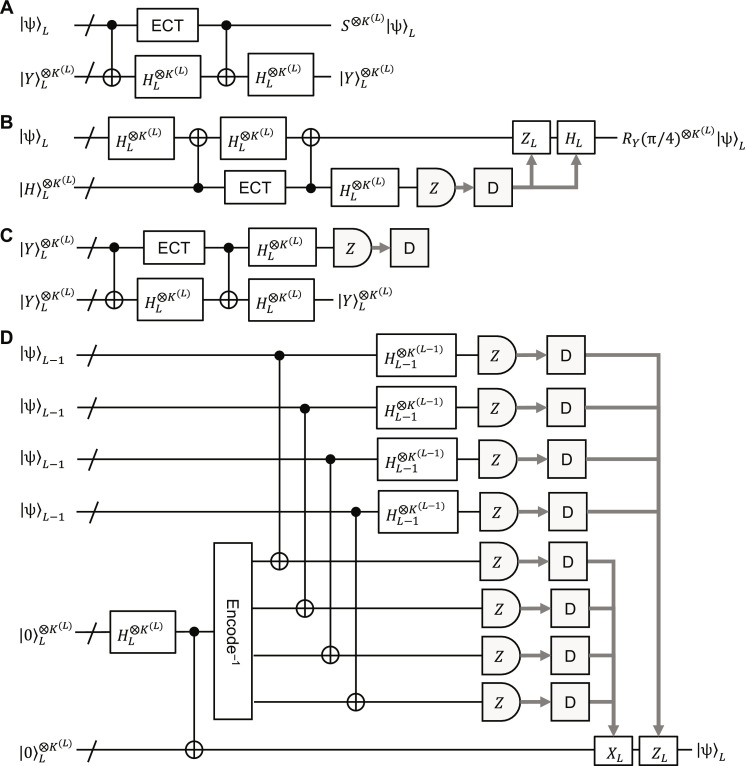

In such a circuit-level noise model, we cannot use the non-fault-tolerant encoders in Fig. 1 (A and B) because of undetectable correlated errors due to CNOT gates in a code block. We thus modify the zero-state encoder at each level as follows. In the following, we use various kinds of error detection and repeat encoding until no error is detected.

For the encoding of the level-1 all-zero state, which is the six-qubit GHZ state as shown in Eq. 5, we can use the well-known fault-tolerant GHZ-state preparation method with an ancilla qubit shown in Fig. 5A. We accept the encoding if the measurement outcome of the ancilla qubit is 0, otherwise reject and restart it from the beginning. Thus, logical X errors can be eliminated. (Logical Z errors do not occur on the logical all-zero state.) To evaluate the space and time overheads for the zero-state encoders, here we introduce the total number of physical qubits including ancilla ones, N′(L), and the circuit depth including state preparation and measurement, T(L), respectively, required for the level-L zero-state encoder. From Fig. 5A, we obtain

| (20) |

Fig. 5. Fault-tolerant zero-state encoders of the many-hypercube codes.

(A) Level-1 zero-state encoder. The inputs are seven physical qubits in zero states. The CNOT and Hadamard gates are physical ones. (B) Level-2 zero-state encoder. The measurement outcomes of the level-1 encoded ancilla qubits are obtained by decoding the physical-qubit outcomes with the hard-decision decoding for error detection (see Materials and Methods). The encoding is repeated until no error is detected and all the level-1 outcomes are 0. (C and D) Level-1 Z-error and X-error detection gadgets (EDZL1 and EDXL1), respectively, used for the level-2 zero-state encoder in (B). Errors are detected unless both the measurement outcomes of the two ancilla qubits are 0. (E and F) Level-2 Z-error and X-error detection gadgets (EDZL2 and EDXL2), respectively, used for the level-3 zero-state encoder. Errors are detected unless none of the outcomes of the minimum distance decoding for error detection with LD = 1 is F (see Materials and Methods). (G) Level-4 zero-state encoder. EDTL3 denotes a level-3 EDT gadget, where the minimum distance decoding for error detection with LD = 2 is used (see Materials and Methods). The same decoding is used for decoding the measurement outcomes of the two ancilla registers. The encoding is repeated until no error is detected and all the parities of the outcomes of the level-3 encoded-qubit pairs in the two ancilla registers are even, where if both the outcomes of a pair are 1, we perform encoded X gates on the first half of the six level-3 encoded qubits.

We cannot apply this method directly to level 2 because of uncorrectable intrablock errors. Also, the low-depth circuit for the GHZ-state preparation in Fig. 5A results in many error-detection gadgets to eliminate the intrablock Z errors. To achieve fault tolerance with minimum effort at level 2, we propose the level-2 zero-state encoder shown in Fig. 5B, where the control qubits of the CNOT gates concentrate on a single qubit to eliminate the intrablock Z errors by a single error-detection gadget. To eliminate intrablock and logical X errors, we also need only a single error-detection gadget and ancilla-qubit measurement. To minimize space overheads, the level-1 error-detection gadgets are implemented by the flag-based method with two physical ancilla qubits and depth 12 in Fig. 5 (C and D) (68). The transversal encoded CNOT and Hadamard gates can be performed fault-tolerantly by transversal physical gates with depths 1 and 2, respectively, as shown in Fig. 1 (D and E). Optimizing the overlaps of physical operations to minimize the time overhead, we obtain

| (21) |

Note that the space overhead, i.e., the total number of physical qubits, can be reduced by reusing the ancilla qubits, but then the time overhead will increase. Also note that we can use the Steane method with an encoded ancilla qubit (69) for the error-detection gadgets, which, in the level-2 case, are shown in Fig. 5 (E and F), but this results in larger space overheads and no performance improvement (see the Supplementary Materials). This is because, at level 1, we only need to measure just a single weight-6 stabilizer, which can be achieved most easily by the flag-based method.

The level-3 zero-state encoder is the same as the level-2 one in Fig. 5B if the levels are raised by one, but level-2 error-detection gadgets are implemented by the above-mentioned Steane method (69) shown in Fig. 5 (E and F). This is because, at level 2, we need to measure six weight-6 level-1 stabilizers and four weight-12 level-2 stabilizers, which can be achieved by the Steane method more easily than the Shor method with physical ancilla qubits. From Fig. 5 (B, E, and F), we obtain

| (22) |

where, and in the following, decoding is not counted for time-overhead evaluation.

Although the encoder in Fig. 5B can also be applied to the level-4 case, then the acceptance probabilities at error-detection gadgets become too low if we use the most stringent condition for error detection. To mitigate this issue, we can relax the error-detection condition (see Materials and Methods), but then the logical gate performance becomes low. (See the Supplementary Materials for the results using the encoder in Fig. 5B at level 4.) To improve the performance, we propose the level-4 zero-state encoder shown in Fig. 5G, which uses two level-3 four-qubit GHZ states with error-detecting teleportation (EDT) gadgets eliminating intrablock Z and X errors simultaneously. The reason why this encoder can achieve higher performance than that in Fig. 5B is that the intrablock errors in two four-qubit GHZ states are independent and therefore detectable with high probability by the ancilla measurements. From Figs. 3 and 5G, we obtain

| (23) |

where, and in the following, Pauli operations are not counted for time-overhead evaluation.

As numerically shown below, the encoders in Fig. 5 well satisfy fault tolerance. The time overheads evaluated above are almost proportional to the level. (The effect of postselection at error-detection gadgets is discussed later.) On the other hand, the logical-gate error rates decrease doubly exponentially with respect to the level, as numerically shown later. These facts suggest that the encoding only needs doubly logarithmic time overheads with respect to computational size and hence is time efficient (44). Although the space overheads increase more rapidly, the net encoding rates defined by K(L)/N′(L) including ancilla qubits are still relatively high, higher than 4% even at level 4. (The encoding rate for the same-distance surface code is 1/162 ≃ 0.4% even without ancilla qubits.) Further optimization of the space and time overheads may be possible but is left for future work.

The comparison with the C4/C6 scheme (45, 65) is as follows. The parameters of the C4/C6 scheme are given by N(L) = 4 × 3L−1, K(L) = 1 (or 2), D(L) = 2L, and N′(L) = 4 × 12L−1 (65). By a similar technique to the one for the GHZ states in Fig. 5G, the number of physical qubits may be reduced to N′(L) = 5L. Then, the net encoding rate at level 4 is K(4)/N′(4) = 0.16% (or 0.32%), which is much lower than that of the level-4 many-hypercube code, as expected. On the other hand, the logical CNOT performance of the C4/C6 scheme (65) is much higher than that of the many-hypercube codes presented below. This may be due to the high rates of the many-hypercube codes and the optimal (block-MAP) decoder for the C4/C6 scheme.

Logical gate operations

Arbitrary encoded Pauli gates can easily be performed fault-tolerantly by physical Pauli gates [or the so-called Pauli frame (45, 66)] according to the definitions of the encoded Pauli operators, e.g., in Eqs. 12 and 13.

Logical SWAP gates can also be performed easily by physical SWAP gates or renumbering of physical qubits as follows. The level-1 encoded SWAP gates are performed as shown in Fig. 1C.At higher levels, e.g., at level 3, simultaneous physical SWAP gates {Q1,j,k ↔ Q3,j,k∣j,k = 1, …,6} result in simultaneouslogical SWAP gates Similarly, and are performed by corresponding simultaneous physical SWAP gates, {Qi,4,k ↔ Qi,6,k ∣ i,k = 1, …,6} and {(Qi,j,1, Qi,j,2, Qi,j,3) ↔ (Qi,j,4, Qi,j,5, Qi,j,6) ∣ i, j = 1, …,6}, respectively. In general, we can perform simultaneous logical SWAP gates between the logical qubits corresponding to the hypercubes on two parallel hyperplanes by simultaneous physical SWAP gates.

For the other gates necessary for universal computation (see Materials and Methods), we first consider the case where the same gate is performed on all the encoded/physical qubits in a code block, which we refer to as full transversal gates. If the same gate is performed on only some specified qubits in a code block, then we call it partial transversal gates, which is harder to implement.

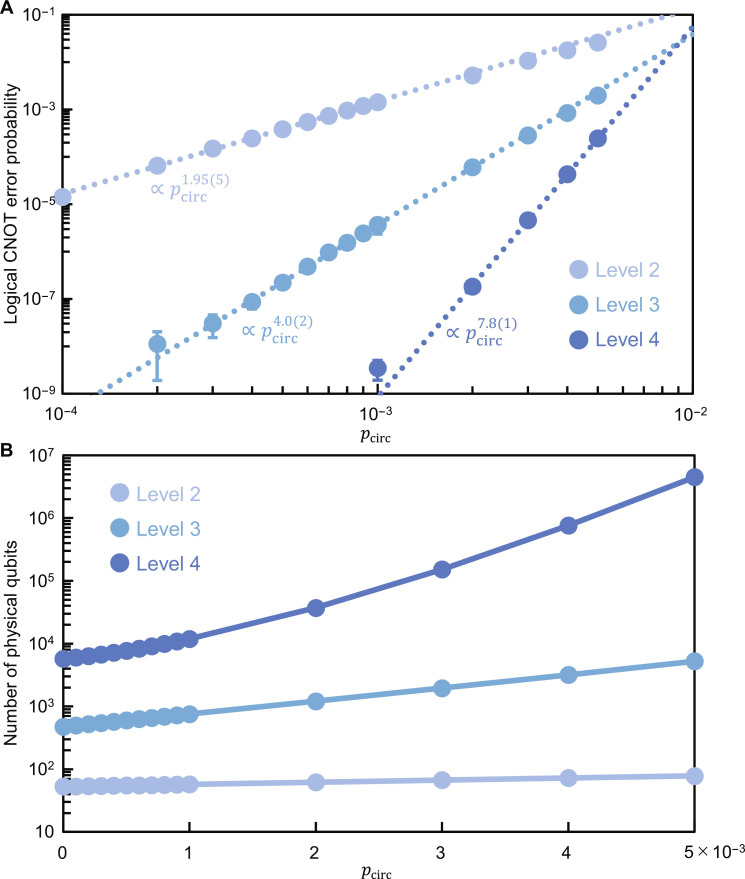

From Fig. 1 (D and E), full transversal logical CNOT and Hadamard gates can be performed fault-tolerantly by full transversal physical CNOT and Hadamard gates (and physical SWAP gates) followed by ECT gadgets. Their time overheads are dominated by the ECT gadgets, which are estimated at T(L) + 7 in the level-L case from Fig. 3 and therefore time efficient. We numerically evaluated the performance of the full transversal logical CNOT gates using the above-mentioned circuit-level noise model (see Materials and Methods for details). The logical CNOT error probabilities estimated by the simulation are shown in Fig. 6A. The error threshold is estimated at 0.9%, which is comparable to the surface code (1.1%) (70) and a recently developed qLDPC quantum memory (0.7%) (40). Also, the exponents of the power-function fits are close to half the code distance, showing that the logical CNOT gates (and the zero-state encoders in Fig. 5) well satisfy fault tolerance. (The level-4 value at pcirc = 10−3 seems an outlier, resulting in a smaller exponent, e.g., 7, in the range of pcirc ≤ 10−3 than that estimated by fitting, 7.8, shown in Fig. 6A. The exponent smaller than half the code distance may be due to the relaxation of the error-detection condition mentioned above.)

Fig. 6. Performance of full transversal logical CNOT gates for the many-hypercube codes in the circuit-level error model.

(A) Each circle shows the error probability per logical CNOT gate for error rate pcirc. The dotted lines are power-function fits to the five data points from the lowest, from which the exponents are estimated. (B) Total number of physical qubits required for the preparation of a logical all-zero state. See Materials and Methods for the details of the simulation and the main text for the definition of the error model.

In the above simulation of logical CNOT gates, we also estimated the expectation value of N′(L) taking the effect of postselection and restart into account. The results are shown in Fig. 6B. It turns out that we need pcirc ≤ 10−3 to keep the space-overhead increase rate due to postselection less than 2 even at level 4. This will be achievable for ion-trap and neutral-atom systems (38).

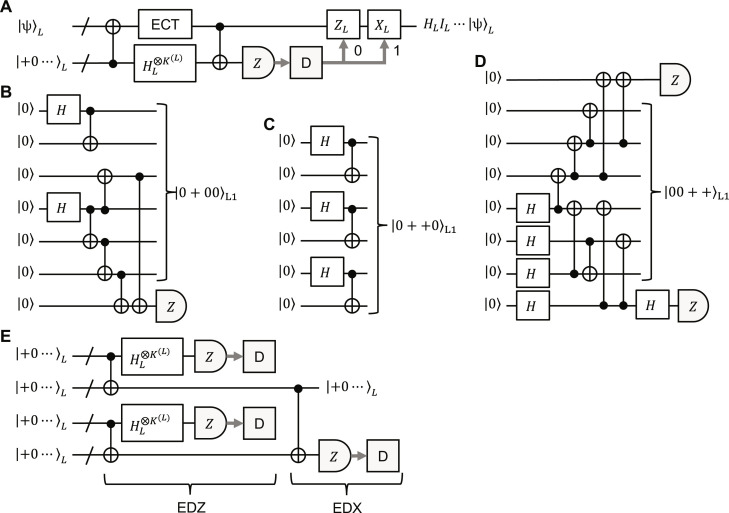

Next, we consider full transversal logical phase and non-Clifford gates, S and RY(π/4) (see Materials and Methods for their definitions). It is known that these two gates can be performed using ancilla qubits in and , respectively, together with CNOT and Hadamard gates (see Fig. 7, A and B), where |Y⟩ and |H⟩ are the eigenstates of Y and H, respectively, with eigenvalue 1 (15, 71). Therefore, the full transversal logical S and RY(π/4) require to fault-tolerantly prepare the level-L logical and , which can be achieved by non-fault-tolerant encoding with the arbitrary-state encoder in Fig. 1B followed by state distillation and level-raising teleportation, as originally proposed for the C4/C6 scheme (71). (The full transversal logical non-Clifford gates also need partial transversal logical Hadamard gates depending on the measurement outcomes, which are explained later.) We propose the 2-to-1 distillation method for based on HS|Y⟩ = |1⟩ shown in Fig. 7C. Note that our method needs only two noisy , unlike the well-known 7-to-1 distillation method with the Steane code (15). This difference comes from the fact that the many-hypercube codes are based on distance-2 codes and therefore do not need distance-3 codes, such as the Steane code, for distillation. For , we can use, e.g., the standard 14-to-2 distillation method based on the distance-2 H6 code (71, 72). The level-raising teleportation shown in Fig. 7D can convert four distilled and to and , respectively, in a fault-tolerant manner (71).

Fig. 7. Logical phase and non-Clifford gates.

(A and B) Full transversal logical phase and non-Clifford gates, S and RY(π/4), respectively. In (B), the measurement outcomes are decoded, and the logical Z and H are performed if the corresponding decoding outcome is 1. (C) Proposed 2-to-1 distillation for . The distillation is accepted if all the decoding outcomes are 1. (D) Level-raising teleportation. The box “Encode−1” is the gadget performing the inversion of the arbitrary-state encoder in Fig. 1B, outputting four level-(L−1) states, where the other two level-(L−1) blocks are measured and decoded by an error-detection decoder, and the Bell-state preparation is repeated until no error is detected and all the decoding outcomes are 0. In the Bell measurements, the measurement outcomes are also decoded by an error-detection decoder (71).

In the following, we consider partial transversal logical gates. using an ancilla register where some logical qubits are in and the others in |0⟩, which we refer to as partial |+⟩ states, together with full transversal logical CNOT and Hadamard gates and an ECT gadget, as shown in Fig. 8A. (The ECT gadget is necessary to prevent intrablock errors from spreading through the logical CNOT and Hadamard gates.) Logical partial |+⟩ states can be prepared fault-tolerantly in a similar manner to and explained above. At level 1, we can fault-tolerantly prepare encoded partial |+⟩ states more efficiently than state distillation, as follows. Any level-1 encoded partial |+⟩ state can be prepared by one of the three methods in Fig. 8 (B to D). The first and second encoders in Fig. 8 (B and C) are based on the fact that some level-1 partial |+⟩ states can be expressed with only the Bell state, , and the four-qubit GHZ state by definition. The third encoder in Fig. 8D is obtained from the arbitrary encoder in Fig. 1B followed by verification with minimum effort through the measurements of an encoded Z operator and an encoded X operator, in a similar manner to the most efficient fault-tolerant Steane-code encoder with a single ancilla qubit (73). Applying the level-raising teleportation to the resultant level-1 partial |+⟩ states, we obtain level-2 partial |+⟩ states. At higher levels, we use the 4-to-1 distillation method shown in Fig. 8E.

Fig. 8. Partial transversal logical Hadamard gates.

(A) Partial transversal logical Hadamard gates with a logical partial |+⟩ state and full transversal logical CNOT and Hadamard gates. The logical Z (X) is performed if the decoding outcome is 0 (1). (B to D) Fault-tolerant preparation methods for level-1 logical partial |+⟩ states. The other ones can also be prepared similarly to one of the three through SWAP gates and full transversal Hadamard gates. (E) 4-to-1 distillation for a logical partial |+⟩ state. This is repeated until no error is detected and all the decoding outcomes are consistent with the input state.

The total number of physical qubits and circuit depth for the preparation of a level-L logical partial |+⟩ state, which are denoted by and , respectively, are estimated from Figs. 7D and 8 (D and E) in the worst-case scenario where all the level-1 blocks are encoded by the encoder in Fig. 8D as follows

| (24) |

| (25) |

| (26) |

| (27) |

Although this preparation is time efficient, the space overheads are considerably larger than those for the encoded all-zero states. More efficient encoding of partial |+⟩ states may be possible but left for future work.

From Fig. 7 (A and B), we can perform partial transversal logical S and RY(π/4) by replacing the full transversal logical Hadamard gates with partial ones explained above because then the two logical CNOT gates on the qubits without logical Hadamard gates are cancelled out.

Partial transversal logical CNOT gates between two registers (interblock logical CNOT gates) can be performed using two ancilla registers in the same partial |+⟩ state and full transversal logical CNOT and Hadamard gates, as shown in Fig. 9A. In this case, each logical CNOT gate is performed on the corresponding two logical qubits with the same label in the two registers. Using logical SWAP gates explained above, we can perform at least a logical CNOT gate on an arbitrary logical-qubit pair between the two registers. Last, logical CNOT gates in a register (intrablock logical CNOT gates) can be performed with an ancilla register in the logical all-zero state, logical SWAP gates, and interblock full and partial transversal logical CNOT gates, as shown in Fig. 9B.

Fig. 9. Logical CNOT gates.

(A) Interblock partial transversal logical CNOT gates with two ancilla registers in the same partial |+⟩ states. The Z and X are performed if the corresponding decoding outcome is 1. Then, the logical CNOT gates denoted by UCNOT are performed on the logical qubits corresponding to |+⟩ of the partial |+⟩ state in the control and target states, |ψc⟩ and |ψt⟩, respectively. (B) Intrablock logical CNOT gates using an ancilla register in the logical all-zero state. The first and third CNOT gates highlighted in red are partial transversal logical CNOT gates on the control qubits of the logical CNOT gates to be performed on |ψ⟩L. (The second one is full transversal logical CNOT gates.) The SWAP gate moves the logical qubits corresponding to the control qubits to the ones corresponding to the target qubits of the logical CNOT gates to be performed. They are returned to the original positions by the SWAP−1 gate. Thus, the desired intrablock logical CNOT gates denoted by UCNOT are performed on |ψ⟩L.

Thus, we can implement a universal gate set for the many-hypercube codes fault-tolerantly and perform most of them in parallel. For qLDPC codes, we can, in principle, achieve parallel execution of logical gates in a similar manner, but then logical ancilla states required for it are difficult to prepare, which may need another high-threshold code such as concatenated Steane codes (18). To overcome the ancilla-preparation issue, a current standard approach to logical gates for qLDPC codes uses the teleportation between a logical qubit in a qLDPC quantum memory and another logical qubit encoded with, e.g., the surface code (39, 40), where logical gates are performed on the surface-code logical qubits. Then, however, parallel execution of N logical gates requires at least N surface-code logical qubits, leading to large overheads for large N. Thus, parallel execution of logical gates for qLDPC codes is still challenging. On the other hand, for high-rate concatenated codes, such as the many-hypercube codes and the concatenated quantum Hamming codes (44), the required ancilla states themselves are encoded with the same high-rate concatenated codes and therefore relatively easy to prepare in a step-by-step manner. This is the advantage of high-rate concatenated codes.

DISCUSSION

We have proposed concatenated high-rate quantum error-detecting codes as a family of high-rate quantum codes for fault-tolerant quantum computing. Because the simple code structure allows for a geometrical interpretation using hypercubes corresponding to logical qubits, we call them many-hypercube codes. The encoding rates are remarkably high, 30 and 20% (64 and 256 logical qubits are encoded into 216 and 1296 physical qubits, respectively) for the code distances of 8 and 16, respectively. We have developed a high-performance decoder and fault-tolerant zero-state encoders dedicated to the codes. Using them, we have achieved high error thresholds: 5.6% for bit-flip errors and 0.9% for a logical CNOT gate in a circuit-level noise model. Further improvements of the decoder and encoders for the many-hypercube codes are challenging but desirable. We have also explained how to implement logical gates necessary for universal quantum computation. More efficient logical-gate implementations for the many-hypercube codes may be possible but are left for future work. Minimizing the number of logical gates and computational depth for given quantum circuits is also an important compilation problem for the many-hypercube codes.

MATERIALS AND METHODS

Elementary gates

In the Z basis {|0⟩, |1⟩}, the matrix representations of elementary gates for universal quantum computation are as follows (3)

Identity gate:

Pauli gates:

Hadamard gate:

Phase gate:

Non-Clifford gate:

CNOT gate:

Hard-decision decoding of the many-hypercube codes

The hard-decision decoding of, e.g., the level-3 many-hypercube code is done as follows (65). The measurement outcomes of physical qubits in each level-1 block and the corresponding level-1 outcomes are denoted by {xi,j,k ∣ i = 1, …,6} and , respectively (j,k = 1, …,6). All the four are set to F (flag indicating an error) if the parity of the six bits, {xi,j,k ∣ i = 1, …,6}, is odd, according to the Z stabilizer. Otherwise, they are set according to the definition of the logical Z operators in Eqs. 1 to 4 as follows: , , , and (mod 2). Next, using the level-1 outcomes in each level-2 block, , we obtain the corresponding level-2 outcomes, , as follows. If there is a single F in the six , e.g., , then we can correct this as (mod 2) according to the Z stabilizer. (Note that error-detecting codes can correct a located error.) Then, the four are set according to the definition of the logical Z operator, as above. If there is no F and the parity of the six bits is even, then we set the four similarly. Otherwise, we set all the four to F. Applying this decoding recursively, we lastly obtain the logical-level outcomes. If it is F, then we randomly choose 0 or 1. For error detection used in the proposed encoders, the decoder returns F (indicating detected errors) unless no F is obtained throughout the decoding.

Symbol-MAP decoding of the many-hypercube code

In the symbol-MAP decoding, we calculate marginal probabilities for each logical qubit, which can be done efficiently. For example, the symbol-MAP decoding of the level-3 many-hypercube code is vthe physical-qubit measurement outcomes {xi,j,k ∣ i = 1, …,6}, the a posteriori probability for a physical-qubit value x is expressed as

| (28) |

where I(A) is the indicator function that returns 1 if A is true and otherwise 0. Then, the marginal a posteriori probability for a level-1 qubit, e.g., , is given by

| (29) |

| (30) |

where the summation in the indicator functions is modulo 2. Repeating such calculations recursively, we lastly obtain the marginal a posteriori probabilities for the logical-qubit values . If , then we set to 0 and otherwise to 1.

Level-by-level minimum distance decoding of the many-hypercube code

The minimum distance decoding is known as one of the highest-performance decoding methods, where we search for a codeword closest to the measurement outcomes in the sense of the Hamming distance. However, there are an exponentially large number of codewords in general; hence, it is usually intractable to find such a minimum-distance codeword. To solve this issue, we keep only minimum-distance codewords and discard larger-distance ones at each level from level 1 to the logical level. Because each level-1 codeword (a bit string corresponding to a level-1 computational-basis state, e.g., 000000 or 111111 for |0000⟩L; see Eq. 5) consists of only six bits, we can easily select minimum-distance codewords and corresponding encoded bit strings (e.g., 0000 for |0000⟩L) in each level-1 block. While there is a single minimum-distance codeword (encoded bit string) when the parity of the six bits is even, there are six minimum-distance codewords (encoded bit strings) when the parity is odd. To construct level-2 codewords using the level-1 minimum-distance encoded bit strings, we first choose five level-1 blocks from the six ones of each level-2 block and then pick one of the minimum-distance encoded bit strings from each of the five level-1 blocks. The encoded bit string of the other level-1 block is automatically determined by the parity-check condition corresponding to the Z stabilizer. In general, the determined encoded bit string is not included in the minimum-distance ones of this block. Therefore, we evaluate the distance of this encoded bit string. Then, we obtain the distance of the level-2 block by summing the distances of the six level-1 blocks. We select the minimum-distance codewords (encoded bit strings) of the level-2 block among all the choices of the five level-1 blocks and their encoded bit strings and keep only them as minimum-distance candidates at level 2. This is our strategy to use the minimum-distance candidates while satisfying the parity-check condition. Doing this selection recursively, we lastly obtain the minimum-distance candidates at the logical level. If we have multiple candidates at the logical level, then we randomly choose one of them. See the Supplementary Materials for more details of this decoding method. For error detection used in the proposed encoders, the decoder returns F unless all the numbers of the candidates at the levels from LD to L are one, where L is the logical level and LD (≤L) is chosen appropriately. The most stringent condition for error detection is given by LD = 1. To increase the acceptance probabilities at error-detection gadgets in the level-4 zero-state encoder, we relax the condition by setting LD as LD = 2.

Simulation of the bit-flip error model

To evaluate the performance of the decoders, we did the following numerical Monte Carlo simulation. We first prepare error-free logical zero states of the many-hypercube code using the encoder in Fig. 1A. Then, independent physical-qubit bit-flip errors are induced with probability pflip per physical qubit. Last, we ideally measure the physical qubits in the Z basis. This quantum circuit includes measurements only at the end. Therefore, we can use the fast sampler of Stim (67) to obtain the physical-qubit measurement outcomes. Then, we decode the outcomes using our homemade Python codes implementing the above-mentioned decoding methods. If all the logical-qubit outcomes are 0, then the decoding succeeds and otherwise fails. We evaluated the decoding error probabilities by sufficiently many trials of this simulation; the numbers of which are provided in table S1.

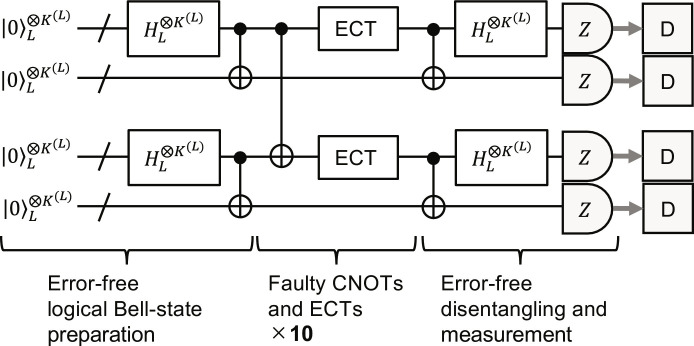

Simulation of logical CNOT gates

To evaluate the performance of full transversal logical CNOT gates in the circuit-level noise model, we did the numerical Monte Carlo simulation shown in Fig. 10. In this simulation, we first prepare two error-free logical Bell-state blocks using the zero-state encoder in Fig. 1A and error-free physical CNOT and Hadamard gates. Then, we perform faulty full transversal logical CNOT gates implemented by faulty full transversal physical CNOT gates on the first code blocks of the two Bell-state blocks. This is followed by ECT gadgets in which physical operations are faulty according to the noise model. The faulty logical CNOT gates with faulty ECT gadgets are repeated 10 times. After that, the Bell states are disentangled and converted to the logical zero states by error-free physical CNOT and Hadamard gates. Last, the logical zero states are ideally measured in the Z basis and the measurement outcomes are decoded by the proposed minimum-distance decoder. Unlike the above simulation of bit-flip errors, this simulation requires mid-circuit measurements and feed-forward operations based on the measurement outcomes. Therefore, we use the slow Tableau Simulator of Stim (67) for stabilizer quantum-circuit simulation parts. From many trials of this simulation, the numbers of which are provided in table S2, we estimate the error probability and its standard error of 10 sets of full transversal logical CNOT gates, which are denoted by p10 and Δ10, respectively. Then, we evaluate those for one set, which are denoted by p1 and Δ1, as and . Because each set includes K(L) logical CNOT gates at level L, we lastly evaluate the error probability and its standard error per logical CNOT gate denoted by pCNOT and ΔCNOT as and .

Fig. 10. Simulation of logical CNOT gates.

We first prepare two sets of error-free logical Bell states encoded with the level-L many-hypercube code in four registers. Then, we perform 10 times faulty full transversal logical CNOT gates (implemented by faulty full transversal physical CNOT gates) followed by faulty ECT gadgets on the first and third registers in the circuit-level noise model. Last, we disentangle the logical states by error-free operations and ideally measure all the physical qubits in the Z basis. The measurement outcomes are decoded by the minimum distance decoder. If all the logical outputs are 0, then the 10 sets of full transversal logical CNOT gates succeed and otherwise fail.

Acknowledgments

Parts of numerical simulations were done on the HOKUSAI supercomputer at RIKEN (project IDs Q23614 and RB230022).

Funding: H.G. acknowledges that he received no funding in support of this research.

Author contributions: H.G. conceived the idea, constructed the many-hypercube codes, found its geometrical interpretation, developed the decoders and encoders, established the methods for logical gates with the many-hypercube codes, did all the simulations, and wrote the manuscript.

Competing interests: H.G. is an inventor on a Japanese patent application related to this work filed by RIKEN (no. P2024-031469, filed 1 March 2024). The author declares that he has no other competing interests.

Data and materials availability: All data needed to evaluate the conclusions in the paper are present in the paper and/or the Supplementary Materials.

Supplementary Materials

This PDF file includes:

Supplementary Text

Figs. S1 to S6

Tables S1 to S3

REFERENCES AND NOTES

- 1.P. W. Shor, Fault-tolerant quantum computation, in Proceedings of the 37th Symposium on Foundations of Computer Science (IEEE Computer Society Press, 1996), pp. 56–65. [Google Scholar]

- 2.Gottesman D., Theory of fault-tolerant quantum computation. Phys. Rev. A 57, 127–137 (1998). [Google Scholar]

- 3.M. A. Nielsen, I. L. Chuang, Quantum Computation and Quantum Information (Cambridge Univ. Press, 2000). [Google Scholar]

- 4.S. B. Bravyi, A. Y. Kitaev, Quantum codes on a lattice with boundary. arXiv:quant-ph/9811052 (1998).

- 5.Dennis E., Kitaev A., Landahl A., Preskill J., Topological quantum memory. J. Math. Phys. 43, 4452–4505 (2002). [Google Scholar]

- 6.Raussendorf R., Harrington J., Fault-tolerant quantum computation with high threshold in two dimensions. Phys. Rev. Lett. 98, 190504 (2007). [DOI] [PubMed] [Google Scholar]

- 7.Raussendorf R., Harrington J., Goyal K., Topological fault-tolerance in cluster state quantum computation. New J. Phys. 9, 199 (2007). [Google Scholar]

- 8.Fowler A. G., Stephens A. M., Groszkowski P., High-threshold universal quantum computation on the surface code. Phys. Rev. A 80, 052312 (2009). [Google Scholar]

- 9.Horsman D., Fowler A. G., Devitt S., Van Meter R., Surface code quantum computing by lattice surgery. New J. Phys. 14, 123011 (2012). [Google Scholar]

- 10.Terhal B. M., Quantum error correction for quantum memories. Rev. Mod. Phys. 87, 307–346 (2015). [Google Scholar]

- 11.Krinner S., Lacroix N., Remm A., Di Paolo A., Genois E., Leroux C., Hellings C., Lazar S., Swiadek F., Herrmann J., Norris G. J., Andersen C. K., Müller M., Blais A., Eichler C., Wallraff A., Realizing repeated quantum error correction in a distance-three surface code. Nature 605, 669–674 (2022). [DOI] [PubMed] [Google Scholar]

- 12.Zhao Y., Ye Y., Huang H.-L., Zhang Y., Wu D., Guan H., Zhu Q., Wei Z., He T., Cao S., Chen F., Chung T.-H., Deng H., Fan D., Gong M., Guo C., Guo S., Han L., Li N., Li S., Li Y., Liang F., Lin J., Qian H., Rong H., Su H., Sun L., Wang S., Wu Y., Xu Y., Ying C., Yu J., Zha C., Zhang K., Huo Y.-H., Lu C.-Y., Peng C.-Z., Zhu X., Pan J.-W., Realization of an error-correcting surface code with superconducting qubits. Phys. Rev. Lett. 129, 030501 (2022). [DOI] [PubMed] [Google Scholar]

- 13.Google Quantum AI , Suppressing quantum errors by scaling a surface code logical qubit. Nature 614, 676–681 (2023). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 14.Jones N. C., Van Meter R., Fowler A. G., McMahon P. L., Kim J., Ladd T. D., Yamamoto Y., Layered architecture for quantum computing. Phys. Rev. X 2, 031007 (2012). [Google Scholar]

- 15.Fowler A. G., Mariantoni M., Martinis J. M., Cleland A. N., Surface codes: Towards practical large-scale quantum computation. Phys. Rev. A 86, 032324 (2012). [Google Scholar]

- 16.Gidney C., Ekerå M., How to factor 2048 bit RSA integers in 8 hours using 20 million noisy qubits. Quantum 5, 433 (2021). [Google Scholar]

- 17.Breuckmann N. P., Eberhardt J. N., Quantum low-density parity-check codes. PRX Quantum 2, 040101 (2021). [Google Scholar]

- 18.Gottesman D., Fault-tolerant quantum computation with constant overhead. Quantum Inf. Comput. 14, 1338–1372 (2014). [Google Scholar]

- 19.D. Gottesman, Opportunities and challenges in fault-tolerant quantum computation. arXiv:2210.15844 [quant-ph] (2022).

- 20.MacKay D. J. C., Mitchison G., McFadden P. L., Sparse-graph codes for quantum error correction. IEEE Trans. Inf. Theory 50, 2315–2330 (2004). [Google Scholar]

- 21.Kovalev A. A., Pryadko L. P., Quantum Kronecker sum-product low-density parity-check codes with finite rate. Phys. Rev. A 88, 012311 (2013). [Google Scholar]

- 22.A. Leverrier, J.-P. Tillich, G. Zemor, Quantum expander codes, in 2015 IEEE 56th Annual Symposium on Foundations of Computer Science (IEEE, 2015), pp. 810–824. [Google Scholar]

- 23.O. Fawzi, A. Grospellier, A. Leverrier, Constant overhead quantum fault-tolerance with quantum expander codes, in 2018 IEEE 59th Annual Symposium on Foundations of Computer Science (FOCS) (IEEE, 2018), pp. 106–114. [Google Scholar]

- 24.Breuckmann N. P., Eberhardt J. N., Balanced product quantum codes. IEEE Trans. Inf. Theory 67, 6653–6674 (2021). [Google Scholar]

- 25.P. Panteleev, G. Kalachev, Asymptotically good quantum and locally testable classical LDPC codes. arXiv:2111.03654 [cs.IT] (2021).

- 26.I. Dinur, M.-H. Hsieh, T.-C. Lin, T. Vidick, Good quantum LDPC codes with linear time decoders, in STOC 2023: Proceedings of the 55th Annual ACM Symposium on Theory of Computing (Association for Computing Machinery, 2023), pp. 905–918. [Google Scholar]

- 27.A. Leverrier, G. Zémor, Quantum Tanner codes, in 2022 IEEE 63rd Annual Symposium on Foundations of Computer Science (FOCS) (IEEE, 2022), pp. 872–883. [Google Scholar]

- 28.T.-C. Lin, M.-H. Hsieh, Good quantum LDPC codes with linear time decoder from lossless expanders. arXiv:2203.03581 [quant-ph] (2022).

- 29.O. Fawzi, A. Grospellier, A. Leverrier, Efficient decoding of random errors for quantum expander codes, in Proceedings of the 50th Annual ACM SIGACT Symposium on Theory of Computing (Association for Computing Machinery, 2018), pp. 521–534. [Google Scholar]

- 30.A. Grospellier, A. Krishna, Numerical study of hypergraph product codes. arXiv:1810.03681 [quant-ph] (2018).

- 31.Roffe J., White D. R., Burton S., Campbell E., Decoding across the quantum low-density parity-check code landscape. Phys. Rev. Res. 2, 043423 (2020). [Google Scholar]

- 32.Panteleev P., Kalachev G., Degenerate quantum LDPC codes with good finite length performance. Quantum 5, 585 (2021). [Google Scholar]

- 33.Grospellier A., Grouès L., Krishna A., Leverrier A., Combining hard and soft decoders for hypergraph product codes. Quantum 5, 432 (2021). [Google Scholar]

- 34.Leverrier A., Zémor G., Decoding quantum Tanner codes. IEEE Trans. Inf. Theory 69, 5100–5115 (2023). [Google Scholar]

- 35.S. Gu, C. A. Pattison, E. Tang, An efficient decoder for a linear distance quantum LDPC code, in STOC 2023: Proceedings of the 55th Annual ACM Symposium on Theory of Computing (Association for Computing Machinery, 2023), pp. 919–932. [Google Scholar]

- 36.Tremblay M. A., Delfosse N., Beverland M. E., Constant-overhead quantum error correction with thin planar connectivity. Phys. Rev. Lett. 129, 050504 (2022). [DOI] [PubMed] [Google Scholar]

- 37.J. Viszlai, W. Yang, S. F. Lin, J. Liu, N. Nottingham, J. M. Baker, F. T. Chong, Matching generalized-bicycle codes to neutral atoms for low-overhead fault-tolerance. arXiv:2311.16980 [quant-ph] (2023).

- 38.C. Poole, T. M. Graham, M. A. Perlin, M. Otten, M. Saffman, Architecture for fast implementation of qLDPC codes with optimized Rydberg gates. arXiv:2404.18809 [quant-ph] (2024).

- 39.Xu Q., Ataides J. P. B., Pattison C. A., Raveendran N., Bluvstein D., Wurtz J., Vasić B., Lukin M. D., Jiang L., Zhou H., Constant-overhead fault-tolerant quantum computation with reconfigurable atom arrays. Nat. Phys. 20, 1084–1090 (2024). [Google Scholar]

- 40.Bravyi S., Cross A. W., Gambetta J. M., Maslov D., Rall P., Yoder T. J., High-threshold and low-overhead fault-tolerant quantum memory. Nature 627, 778–782 (2024). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 41.Krishna A., Poulin D., Fault-tolerant gates on hypergraph product codes. Phys. Rev. X 11, 011023 (2021). [Google Scholar]

- 42.Cohen L. Z., Kim I. H., Bartlett S. D., Brown B. J., Low-overhead fault-tolerant quantum computing using long-range connectivity. Sci. Adv. 8, eabn1717 (2022). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 43.Quintavalle A. O., Webster P., Vasmer M., Partitioning qubits in hypergraph product codes to implement logical gates. Quantum 7, 1153 (2023). [Google Scholar]

- 44.Yamasaki H., Koashi M., Time-efficient constant-space-overhead fault-tolerant quantum computation. Nat. Phys. 20, 247–253 (2024). [Google Scholar]

- 45.Knill E., Quantum computing with realistically noisy devices. Nature 434, 39–44 (2005). [DOI] [PubMed] [Google Scholar]

- 46.S. Yoshida, S. Tamiya, H. Yamasaki, Concatenate codes, save qubits. arXiv:2402.09606 [quant-ph] (2024).

- 47.Bravyi S., Suchara M., Vargo A., Efficient algorithms for maximum likelihood decoding in the surface code. Phys. Rev. A 90, 032326 (2014). [Google Scholar]

- 48.Webster M. A., Quintavalle A. O., Bartlett S. D., Transversal diagonal logical operators for stabiliser codes. New J. Phys. 25, 103018 (2023). [Google Scholar]

- 49.Bombin H., Martin-Delgado M. A., Topological quantum distillation. Phys. Rev. Lett. 97, 180501 (2006). [DOI] [PubMed] [Google Scholar]

- 50.Fowler A. G., Two-dimensional color-code quantum computation. Phys. Rev. A 83, 042310 (2011). [Google Scholar]

- 51.A. J. Landahl, J. T. Anderson, P. R. Rice, Fault-tolerant quantum computing with color codes. arXiv:1108.5738 [quant-ph] (2021).

- 52.A. J. Landahl, C. Ryan-Anderson, Quantum computing by color-code lattice surgery. arXiv:1407.5103 [quant-ph] (2014).

- 53.Ryan-Anderson C., Bohnet J. G., Lee K., Gresh D., Hankin A., Gaebler J. P., Francois D., Chernoguzov A., Lucchetti D., Brown N. C., Gatterman T. M., Halit S. K., Gilmore K., Gerber J. A., Neyenhuis B., Hayes D., Stutz R. P., Realization of real-time fault-tolerant quantum error correction. Phys. Rev. X 11, 041058 (2021). [Google Scholar]

- 54.Postler L., Heuβen S., Pogorelov I., Rispler M., Feldker T., Meth M., Marciniak C. D., Stricker R., Ringbauer M., Blatt R., Schindler P., Müller M., Monz T., Demonstration of fault-tolerant universal quantum gate operations. Nature 605, 675–680 (2022). [DOI] [PubMed] [Google Scholar]

- 55.Y. Wang, S. Simsek, T. M. Gatterman, J. A. Gerber, K. Gilmore, D. Gresh, N. Hewitt, C. V. Horst, M. Matheny, T. Mengle, B. Neyenhuis, B. Criger, Fault-tolerant one-bit addition with the smallest interesting colour code. arXiv:2309.09893 [quant-ph] (2023). [DOI] [PMC free article] [PubMed]

- 56.Self C. N., Benedetti M., Amaro D., Protecting expressive circuits with a quantum error detection code. Nat. Phys. 20, 219–224 (2024). [Google Scholar]

- 57.Yamamoto K., Duffield S., Kikuchi Y., Ramo D. M., Demonstrating Bayesian quantum phase estimation with quantum error detection. Phys. Rev. Res. 6, 013221 (2024). [Google Scholar]

- 58.M. P. da Silva, C. Ryan-Anderson, J. M. Bello-Rivas, A. Chernoguzov, J. M. Dreiling, C. Foltz, F. Frachon, J. P. Gaebler, T. M. Gatterman, L. Grans-Samuelsson, D. Hayes, N. Hewitt, J. Johansen, D. Lucchetti, M. Mills, S. A. Moses, B. Neyenhuis, A. Paz, J. Pino, P. Siegfried, J. Strabley, A. Sundaram, D. Tom, S. J. Wernli, M. Zanner, R. P. Stutz, K. M. Svore, Demonstration of logical qubits and repeated error correction with better-than-physical error rates. arXiv:2404.02280 [quant-ph] (2024).

- 59.C. Ryan-Anderson, N. C. Brown, C. H. Baldwin, J. M. Dreiling, C. Foltz, J. P. Gaebler, T. M. Gatterman, N. Hewitt, C. Holliman, C. V. Horst, J. Johansen, D. Lucchetti, T. Mengle, M. Matheny, Y. Matsuoka, K. Mayer, M. Mills, S. A. Moses, B. Neyenhuis, J. Pino, P. Siegfried, R. P. Stutz, J. Walker, D. Hayes, High-fidelity and fault-tolerant teleportation of a logical qubit using transversal gates and lattice surgery on a trapped-ion quantum computer. arXiv:2404.16728 [quant-ph] (2024).

- 60.Graham T. M., Song Y., Scott J., Poole C., Phuttitarn L., Jooya K., Eichler P., Jiang X., Marra A., Grinkemeyer B., Kwon M., Ebert M., Cherek J., Lichtman M. T., Gillette M., Gilbert J., Bowman D., Ballance T., Campbell C., Dahl E. D., Crawford O., Blunt N. S., Rogers B., Noel T., Saffman M., Multi-qubit entanglement and algorithms on a neutral-atom quantum computer. Nature 604, 457–462 (2022). [DOI] [PubMed] [Google Scholar]

- 61.Bluvstein D., Levine H., Semeghini G., Wang T. T., Ebadi S., Kalinowski M., Keesling A., Maskara N., Pichler H., Greiner M., Vuletić V., Lukin M. D., A quantum processor based on coherent transport of entangled atom arrays. Nature 604, 451–456 (2022). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 62.Evered S. J., Bluvstein D., Kalinowski M., Ebadi S., Manovitz T., Zhou H., Li S. H., Geim A. A., Wang T. T., Maskara N., Levine H., Semeghini G., Greiner M., Vuletić V., Lukin M. D., High-fidelity parallel entangling gates on a neutral-atom quantum computer. Nature 622, 268–272 (2023). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 63.Bluvstein D., Evered S. J., Geim A. A., Li S. H., Zhou H., Manovitz T., Ebadi S., Cain M., Kalinowski M., Hangleiter D., Ataides J. P. B., Maskara N., Cong I., Gao X., Rodriguez P. S., Karolyshyn T., Semeghini G., Gullans M. J., Greiner M., Vuletić V., Lukin M. D., Logical quantum processor based on reconfigurable atom arrays. Nature 626, 58–65 (2024). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 64.Poulin D., Optimal and efficient decoding of concatenated quantum block codes. Phys. Rev. A 74, 052333 (2006). [Google Scholar]

- 65.Goto H., Uchikawa H., Fault-tolerant quantum computation with a soft-decision decoder for error correction and detection by teleportation. Sci. Rep. 3, 2044 (2013). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 66.Knill E., Scalable quantum computing in the presence of large detected-error rates. Phys. Rev. A 71, 042322 (2005). [Google Scholar]

- 67.Gidney C., Stim: A fast stabilizer circuit simulator. Quantum 5, 497 (2021). [Google Scholar]

- 68.Chao R., Reichardt B. W., Quantum error correction with only two extra qubits. Phys. Rev. Lett. 121, 050502 (2018). [DOI] [PubMed] [Google Scholar]

- 69.Steane A. M., Active stabilization, quantum computation, and quantum state synthesis. Phys. Rev. Lett. 78, 2252–2255 (1997). [Google Scholar]

- 70.Wang D. S., Fowler A. G., Hollenberg L. C. L., Surface code quantum computing with error rates over 1%. Phys. Rev. A 83, 020302(R) (2011). [Google Scholar]

- 71.Goto H., Step-by-step magic state encoding for efficient fault-tolerant quantum computation. Sci. Rep. 4, 7501 (2014). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 72.Jones C., Multilevel distillation of magic states for quantum computing. Phys. Rev. A 87, 042305 (2013). [Google Scholar]

- 73.Goto H., Minimizing resource overheads for fault-tolerant preparation of encoded states of the Steane code. Sci. Rep. 6, 19578 (2016). [DOI] [PMC free article] [PubMed] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Supplementary Materials

Supplementary Text

Figs. S1 to S6

Tables S1 to S3