Abstract

Branched nanostructures represent unique, 3D building blocks for the “bottom-up” paradigm of nanoscale science and technology. Here, we report a rational, multistep approach toward the general synthesis of 3D branched nanowire (NW) heterostructures. Single-crystalline semiconductor, including groups IV, III–V, and II–VI, and metal branches have been selectively grown on core or core/shell NW backbones, with the composition, morphology, and doping of core (core/shell) NWs and branch NWs well controlled during synthesis. Measurements made on the different composition branched NW structures demonstrate encoding of functional p-type/n-type diodes and light-emitting diodes (LEDs) as well as field effect transistors with device function localized at the branch/backbone NW junctions. In addition, multibranch/backbone NW structures were synthesized and used to demonstrate capability to create addressable nanoscale LED arrays, logic circuits, and biological sensors. Our work demonstrates a previously undescribed level of structural and functional complexity in NW materials, and more generally, highlights the potential of bottom-up synthesis to yield increasingly complex functional systems in the future.

Keywords: nanodevices, nanoelectronics, nanophotonics, biosensors, designed synthesis

Design and rational synthesis of semiconductor nanowire (NW) building blocks with well-defined structure and physical properties are central to the “bottom-up” approach for nanoscience and nanotechnology (1–6). To date, significant progress has been made in control of morphology, size, and composition on length scales ranging from the atomic and up (1–28). Branched or tree-like NWs, in which one or more secondary NWs grow in a radial direction from a primary NW backbone, represent an especially interesting class of NW structures because branching naturally provides access to higher dimensionality structures and the capability of achieving parallel connectivity and interconnection during synthesis (12, 13). Indeed, well-controlled variations in the composition and/or doping of backbone and branch NWs could make possible the design and realization of unique electronic and photonic nanodevices via encoding functionality synthetically at branch junctions.

Previous studies of branched NW structures have led to several advances. First, original work in 2004 (12, 13) demonstrated the controlled synthesis of Si (12), GaN (12), and GaP (13) branched NWs via a multistep nanocluster-catalyzed vapor–liquid–solid (VLS) process, in which the diameter, length, and density of nanoscale branches were defined independently from backbone NW growth. Several groups have also employed a single-step, chemical vapor transport and condensation strategy to produce a wide range of straight or twisted semiconductor branched NWs, including ZnO (14, 15), WO3 (16), PbS (17), and PbSe (18). These studies have provided additional insight into growth mechanisms of branched nanostructures, but exhibited only limited control of the branch synthesis that is ultimately central to defining functionality for device applications. More recently, the growth of branched heterostructures with different backbone and branch compositions, including ZnSe/CdSe (19) and ZnS/CdS (20, 21), was reported using a multistep approach similar to that described in 2004 (12, 13). This work showed the possibility for encoding distinct composition junctions at branch points through synthesis, but did not demonstrate the critical potential of such branch junctions to serve as electronic and optoelectronic devices. Here, we describe studies that extend in a substantial manner the synthesis of branched NW heterostructures and, significantly, that reveal well-defined electrical and optoelectronic junction properties, including the demonstration of addressable nanoscale light-emitting diode (LED) arrays, logic circuits, and biological sensors.

Results and Discussion

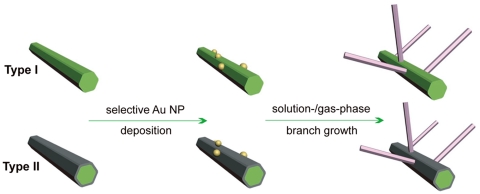

We have focused on two distinct classes of branched NWs, with metal or semiconductor branches grown on either the native surface of semiconductor (type I) or on the oxide surface of core/shell semiconductor/oxide (type II) NW backbones (Fig. 1). The synthesis involves two critical steps following synthesis of the core and core/shell NWs. First, gold nanoparticles (Au-NPs) are selectively deposited onto the respective backbone surfaces using either an in situ solution reduction of  on Si-NW surfaces for type I structures or binding of Au-NPs to the oxide surfaces of Si/SiO2 core/shell NWs for type II structures (see Materials and Methods). Transmission electron microscopy (TEM) images demonstrate that these methods provide uniformly dispersed Au-NPs on the Si (Fig. S1A) and Si/SiO2 (Fig. S1C) NW surfaces, and moreover, high-resolution TEM (HRTEM) images demonstrate intimate contact between Au-NPs and the Si (Fig. S1B) and SiO2 (Fig. S1D) surfaces. Second, the resulting Au-NPs were used as seeds or catalysts to define the nucleation and growth of branch NWs on the backbones using either an aqueous solution-based method for metal branches and vapor-phase approaches for semiconductor branches.

on Si-NW surfaces for type I structures or binding of Au-NPs to the oxide surfaces of Si/SiO2 core/shell NWs for type II structures (see Materials and Methods). Transmission electron microscopy (TEM) images demonstrate that these methods provide uniformly dispersed Au-NPs on the Si (Fig. S1A) and Si/SiO2 (Fig. S1C) NW surfaces, and moreover, high-resolution TEM (HRTEM) images demonstrate intimate contact between Au-NPs and the Si (Fig. S1B) and SiO2 (Fig. S1D) surfaces. Second, the resulting Au-NPs were used as seeds or catalysts to define the nucleation and growth of branch NWs on the backbones using either an aqueous solution-based method for metal branches and vapor-phase approaches for semiconductor branches.

Fig. 1.

Schematic illustrating the general synthesis of branched NW heterostructures. Following the synthesis of bare (type I) or core/shell (type II) NWs, Au-NPs are selectively deposited onto the respective backbone surfaces and then used as seeds or catalysts to define the nucleation and growth of branch NWs on the backbones. Branch NWs are synthesized using established aqueous solution (metal branches) and vapor-phase (semiconductor branches) methods.

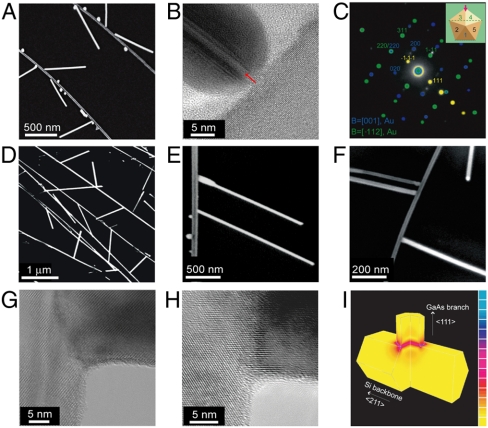

We first examined the growth of metal and semiconductor branch NWs for type I structures. Gold metal branch NWs were grown using a reported surfactant mediated methodology (29) in aqueous solution (see Materials and Methods). A typical SEM image of Si/Au branched NW structures (Fig. 2A) shows that Au branches grown in this manner are uniform with an average diameter of 31 ± 4 nm and average length of 620 ± 100 nm. The overall yield of branches, which was determined with respect to the total number of Au-NP nucleation catalysts, was greater than 40% for these reaction conditions. The average aspect ratio of these Au branches, 20 ± 4, could be further improved by reducing the Au-reactant concentration and/or increasing the surfactant concentration, where the highest value obtained in our studies was ca. 50 (see Materials and Methods).

Fig. 2.

Structural characterization of type I branched NW heterostructures. (A) SEM image of Si/Au branched NWs. (B) HRTEM image of Si/Au branched junction; red arrow highlights twin plane. (C) SAED pattern of the junction region shown in B, where blue and green spots originate from 〈100〉Au, 〈112〉Au zone diffraction, and yellow spots are from the crystalline Si backbone. (Inset) Cross-sectional model of the penta-twinned Au branch consisting of five twinned subunits. Red arrow marks the incident beam direction. (D–F) SEM images of Si/Ge (D), Si/GaAs (E), and Si/GaP (F) branched NWs. (G and H) HRTEM images of Si/Ge (G) and Si/GaAs (H) branched junctions. (I) Simulated von Mises stress field at Si/GaAs branched junction. The scale bar range is from 3.1 × 106 to 1.6 × 1010 Pa.

We further examined the Si/Au-branch NW junction structures in more detail using TEM and selected area electron diffraction (SAED). Low-resolution TEM images of Si/Au branched NW junctions (e.g., Fig. S2A) show that Au NW branches have approximately curved ends that contact the Si-NW backbone surfaces at the central region of the Au-branch NWs. A HRTEM image of the Si/Au junction (Fig. 2B) shows the single-crystalline structure of Si-NW backbone and more complex structure for the Au branch NW. Specifically, the Au branch exhibits modulations in the electron density in the central region of the NW parallel to the direction of branch axis, which are indicative of a twinned structure (29). Indeed, SAED patterns acquired to further illuminate the nature of these features (Fig. 2C) can be indexed as a superposition of 〈112〉 and 〈100〉 zones for face-centered cubic Au (a = 0.408 nm) (29), where the branch NW has overall fivefold twin symmetry (Fig. 2C, Inset). These results and model are consistent with the structure described previously by Murphy and coworkers (29).

We have also synthesized a variety of semiconductor branch NWs by vapor-phase growth, where the Au-NPs function as catalysts in a VLS process (1–3, 30) for branch elongation. SEM images of Si/Ge (Fig. 2D), Si/GaAs (Fig. 2E), and Si/GaP (Fig. 2F) backbone/branch NW structures show the uniform semiconductor branch growth from Si-NW backbones with a yield > 70%. Moreover, our general approach can be extended to the growth of other III–V and II–VI semiconductor branches, including InP, InAs, ZnS, ZnSe, CdS, and CdSe (see Materials and Methods).

TEM images of Si/Ge (Fig. S2B), Si/GaAs (Fig. S2C), and Si/InP (Fig. S2D) show that the interfaces between backbone and branch NWs are clean and abrupt. In addition, energy dispersive X-ray mapping of Si/CdS (Fig. S2F) demonstrates the spatially controlled distributions of Si, Cd, and S in the backbone and branch. We note that the Si backbone is free of CdS homogenous shell coating or islands formation due to the well-controlled nanocluster-catalyzed (30) branch synthesis. In addition, HRTEM studies were carried out to further characterize the Si/semiconductor branched junctions. The HRTEM images of the junctions of Si/Ge (Fig. 2G), Si/GaAs (Fig. 2H), and Si/InP (Fig. S2E) backbone/branch NWs show single-crystalline structures for all backbones and branches. These data also suggest that the backbone/branch interfaces remain structurally coherent in one or more crystallographic directions despite the large lattice mismatches for the bulk crystals (31): 4.2% for Si/Ge, 4.1% for Si/GaAs, and 8.1% for Si/InP).

To further understand strain relaxation in these branched NW structures, we carried out stress field simulations (see Materials and Methods). The simulation result for a Si/GaAs backbone/branch NW structure (Fig. 2I) shows that stresses are significant only in regions near the junctions (especially the junction boundary), of dimensions comparable to 1/4 branch width, and produce deformations of negligible magnitude at distances longer than the diameter of branch from the junction region. The possibility of efficient strain relaxation in branched NW heterostructures could significantly expand our choices for backbone and branch materials, which can enable unique device concepts with enhanced properties.

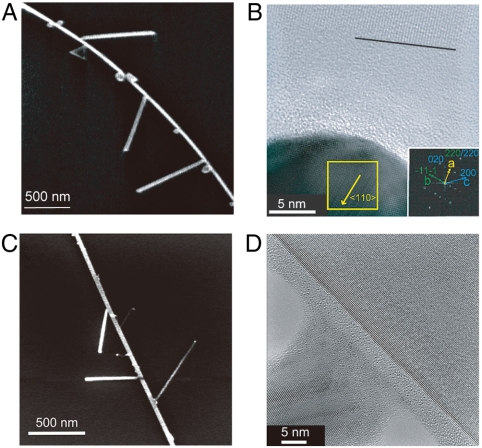

We have also explored a variety of type II branched NW structures because it represents another important category of structural/functional integration, where metal or semiconductor branches can be grown on Si/SiO2 core/shell NW backbones following the same approaches described above. SEM images of Si/SiO2/Au (Fig. 3A) and Si/SiO2/Ge (Fig. 3C) branched NWs exhibit morphologies similar to their respective type I analogs. The HRTEM images of both Si/SiO2/Au (Fig. 3B) and Si/SiO2/Ge (Fig. 3D) branched junctions show clearly an amorphous layer sandwiched between crystalline Si-backbone and branch NWs, which is consistent with our design for type II structures. Analysis of the Au branch last close to the junction (Fig. 3B, Inset) shows the superposition of 〈112〉 and 〈100〉 zone patterns and indicates the Au branch grows along the 〈110〉 direction, the same as in Si/Au branched NWs. We note that the SiO2 shell on these Si-NW backbones can be readily extended to other types of functional materials conformally deposited by atomic layer deposition (32) and has the potential to significantly expand the scope of functionalities defined at the branched junctions.

Fig. 3.

Structural characterization of type II branched NW heterostructures. (A) SEM image of Si/SiO2/Au branched NWs. (B) HRTEM image of Si/SiO2/Au junction. The black line marks the SiO2/Si interface. (Lower Right Inset) FFT pattern from the yellow square region, indexed as a superposition of [001] (blue) and [-112] (green) zone patterns. The marked yellow spot in the FFT pattern is one of the associated double diffraction reflections, where a = b + c. (C and D) SEM (C) and HRTEM (D) images of Si/SiO2/Ge branched NW.

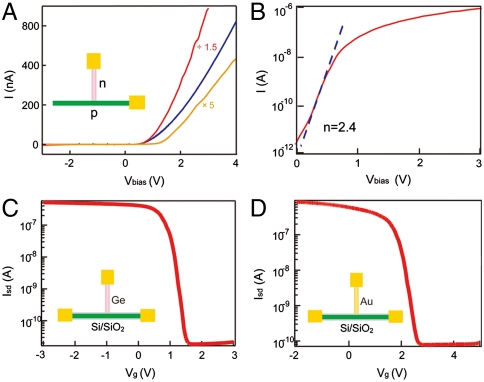

We have fabricated and measured single-branch/backbone NW devices to examine the potential for encoding of functional device properties such as p-n diodes and field effect transistors (FETs) by synthesis (see Materials and Methods; Fig. S3). For example, p-n diodes should be encoded at the junction of p-Si-NW backbone and n-type semiconductor branch, where we have synthesized and studied structures with n-Ge, n-GaAs, and n-CdSe branches. Two-terminal electrical transport measurements recorded on p-Si/n-Ge, p-Si/n-GaAs, and p-Si/n-CdSe backbone/branch NW structures (Fig. 4A) all exhibit clear current rectification with threshold voltages of approximately 1.0 V, consistent with expectations for p-n diode (31). More detailed characterization of the Si/GaAs p-n diode (Fig. 4B) yields a room temperature ideality factor, n, of 2.4. Although the n value indicates surface recombination in the diode (33) and suggests that further optimization could be achieved in the future, the present results nevertheless demonstrate our capability to independently define the doping profile of backbone and branch NWs necessary for encoding device function.

Fig. 4.

Single-branch input devices. (A) Two-terminal I–V characteristics of p-n diodes encoded at p-Si/n-Ge (blue), p-Si/n-GaAs (red), and p-Si/n-CdSe (orange) branched junctions. (B) I–V curve of the same p-Si/n-GaAs diode on semilog scale; the slope (blue dashed line) yields an ideality factor n = 2.4. (C and D) I–Vg curves of nanoscale FETs encoded at p-Si/SiO2/n-Ge (C) and p-Si/SiO2/Au (D) branched junctions, respectively. A source-drain voltage of 0.5 V was used in the measurement.

We have also examined the potential for encoding nanoscale FETs in type II branched NWs, where p-Si-NW backbone serves as the active semiconductor channel, the SiO2 shell layer as the gate dielectric, and heavily doped n-Ge or Au-branch NWs as nanoscale gate electrodes. Source and drain contacts were defined on p-Si-NW backbone, and an additional contact was made at the end of n-Ge or Au branch as voltage input for the gate electrode (Fig. 4 C, Inset, and D, Inset and Fig. S3 B and C). Current (Isd) vs. branch-gate voltage (Vg) data recorded on p-Si/SiO2/n-Ge (Fig. 4C) and p-Si/SiO2/Au (Fig. 4D) branched NW FETs at a source-drain voltage of 0.5 V show a characteristic depletion mode FET behavior (31), with a turnoff current < 100 pA and on/off ratio > 104. The calculated subthreshold slopes for these two nanoscale FET devices are 120 and 150 mV/decade, respectively. The subthreshold values, which indicate good gate coupling, are especially notable given that the gate lengths for the n-Ge and Au-branch devices are only 30 and 35 nm, respectively.

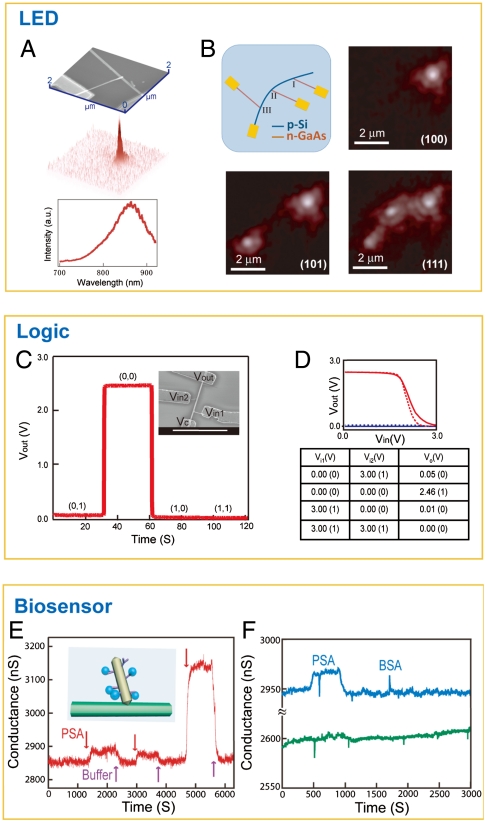

In addition, we have investigated additional functional properties for synthetically encoded branch/backbone NW structures as well as the incorporation of multiple functional branches. First, we have characterized the photonic properties of p-Si/n-GaAs backbone/branch heterostructures, where the direct-band-gap GaAs branch can yield light emission in a forward biased diode (34). Significantly, electroluminescence (EL) data recorded from a p-Si/n-GaAs device (Fig. 5A) exhibits highly localized emission from the branch junction in forward bias, thus making these point-like, nanoscale active emitters (nanoLEDs). The EL spectrum (Fig. 5A, Lower) exhibits a peak maximum at 860 nm, corresponding to the GaAs band-edge emission. We note that the localized emission from the branch junctions was robust; that is, repeated on/off cycles did not affect the emission properties, and studies of over 20 p-Si/n-GaAs nanoLEDs yielded similar results.

Fig. 5.

Multibranch input devices. (A and B) p-Si/n-GaAs branched nanoLEDs. (A) Three-dimensional EL intensity plot (Middle), SEM image (Top), and EL spectrum (Bottom) of a single p-Si/n-GaAs branched nanoLED. (B) Schematic (Upper Left) of an LED array consisting of three p-Si/n-GaAs nanoLEDs, and EL images when a forward bias of 10 V was applied to sequentially turn on one (Upper Right), two (Lower Left), or three (Lower Right) branch junctions. (C and D) NOR logic gate based on two sequential Si/SiO2/Ge branch junctions. (C) The output voltage vs. the four possible logic address level inputs: (0,1), (0,0), (1,0), and (1,1). (Inset) SEM image of the branched device. Scale bar, 2 μm. (D) The output–input (Vo-Vi) relation and experimental truth table for the NOR gate. The solid and dashed red (blue) lines show Vo-Vi1 and Vo-Vi2 when the other input is 0 (1). (E and F) Biological sensor based on Si/Au branched NW FETs. (E) Conductance vs. time curve recorded on a p-Si/Au branched NW sensor with alternate delivery of PSA (4 ng/mL, 80 pg/mL, 200 ng/mL) and pure buffer solutions. The red and purple arrows mark the delivery of protein and buffer solutions into the sensing channel, respectively. (Inset) Schematic of Si/Au branched NW sensor. (F) Conductance vs. time data recorded on Si/Au branched NW sensor with alternating delivery of 4 ng/mL of PSA and 4 μg/mL of BSA solutions (blue curve), and on bare Si-NW device (modified as the Au branches) with delivery of 4 μg/mL of PSA solution (green curve).

We have exploited the reproducibility and robustness of the p-Si/n-GaAs nanoLEDs to study an addressable array consisting of three n-GaAs NW branches on p-Si-NW backbone (Fig. 5B). When a forward bias was applied to turn on one (Fig. 5B, Upper Right), two (Fig. 5B, Lower Left), or three (Fig. 5B, Lower Right) nanoLEDs sequentially, EL measurements demonstrate localized and addressable emission only from the junctions in forward bias. Moreover, we have assembled and characterized seven robust nanoLEDs within a 100 × 100 um2 area (Fig. S4), thus demonstrating the potential of this bottom-up approach for larger-scale integration of these unique photonic devices.

In addition, the concept of synthetically encoding multiple functional branch devices has been used to investigate their potential as logic gates. A two branch input FET configured from a type II Si/SiO2/Ge branched NW structure (Fig. 5C) shows that when either one or both of the inputs were high (3 V) the p-Si-NW backbone FET output was low or off, but when both inputs were low (0 V), the FET output was high. More complete characterization of the input–output characteristics (Fig. 5D) are all consistent with two-input NOR logic gate (35). Similarly, we have also demonstrated OR and AND gates from the integration of p-Si/n-Ge branch diodes (Fig. S5). Overall, these results suggest that the branched and hyperbranched (13) NW structures represent a potentially powerful approach for developing complex logic circuits with some analogy to highly branched and interconnected neuronal systems.

Finally, we investigated the branched NW devices as nanoelectronic sensors for detection of biological molecules (36), where the Au branches can act as “antenna” for analyte after modification with receptors. In contrast to previous studies that modified oxide surfaces of the nanowire and substrate (37, 38), we selectively modified Au branches with antibodies using reactive thiols (see Materials and Methods). Conductance vs. time data recorded from a monoclonal antibody modified p-Si/Au-branch NW FET as prostate specific antigen (PSA) and buffer solutions are delivered to the device (Fig. 5E) demonstrate concentration-dependent binding and unbinding of PSA with a detection limit of 80 pg/mL for signal-to-noise ratio of > 3. Control experiments (Fig. 5F) using BSA and unbranched Si-NW FETs further demonstrate the excellent selectivity of Si/Au-branch NW sensor.

Conclusions

In summary, we report a rational, multistep approach for the general synthesis of branched nanowire heterostructures and demonstrate the encoding of electronic and optoelectronic functions at branched junctions through controlled synthesis. Single-crystalline semiconductors, including groups IV, III–V, and II–VI, and metal branches have been selectively grown on core or core/shell NW backbones via vapor- and solution-phase methods. With precise control over composition and doping, we demonstrate reliable p-n diode, LED, and FET device characteristics encoded at the branch junctions. Furthermore, we have demonstrated the potential to create more complicated structures and functional device-based backbone/multibranch NW structures, including addressable nanoLED arrays, logic circuits, and biological sensors. Our work highlights the power and potential of synthetically encoding functionalities at branch junctions, and more generally, bottom-up synthesis for the development of increasingly complex functional systems in the future.

Materials and Methods

Backbone NW Synthesis.

Si-NW backbones were synthesized using nanocluster-catalyzed chemical vapor deposition method reported previously (39). Si/SiO2 core-shell NWs were prepared by oxidation of Si NWs in pure O2 (flow rate: 50 sccm; pressure: 40 torr) at 700 °C for 1–3 h; the resulting oxide layer thickness was 2–5 nm, respectively.

Selective Deposition of Au Nanoparticles.

Au-NPs were deposited on bare Si NWs by galvanic surface reduction (40). First, Si NWs were etched in 5% hydrogen fluoride solution for 1 min to produce hydrogen-terminated surface, and then resulting Si NWs were immersed in HAuCl4 solution (1 - 5 × 10-5 M) for 5–10 min. The HAuCl4 solution concentration and reaction time was varied to control the Au-NP density and size, with higher HAuCl4 and longer reaction time resulting in larger and denser Au-NPs. Au-NPs were deposited on the SiO2 surfaces of Si/SiO2 core/shell NWs in a two-step process. First, the Si/SiO2 NWs were immersed in 0.1% polylysine solution (molecular weight: 150 k–300 k, Ted Pella) and rinsed thoroughly with deionized water. Second, the polylysine modified NWs were placed in the solution of citrate stabilized Au-NPs (15 nm, 1.4 × 1010/mL, Ted Pella) for 5 min, followed by gentle rinse with deionized water.

Synthesis of Si/Au and Si/SiO2/Au branched NWs.

Si or Si/SiO2 NWs with deposited Au-NPs were dispersed on SiO2 surfaces of Si substrates (600-nm oxide, n-type 0.005 Ω-cm, Nova Electronic Materials) from isopropanol solutions, dried with N2, and then annealed at 200 °C for 10 min. Au branched NWs were then grown by immersing the respective substrates with dispersed NWs in a solution containing HAuCl4 (2 × 10-4 - 1 × 10-3 M), ascorbic acid (4 × 10-4 - 2 × 10-3 M), and cetyl trimethylammonium bromide (CTAB) (0.025–0.1 M) (29) for 12–24 h in the dark. A Au-NW aspect ratio up to 50 can be achieved under optimal growth conditions with 1 × 10-3 M HAuCl4, 2 × 10-3 M ascorbic acid, and 0.1 M CTAB.

Synthesis of Si/semiconductor and Si/SiO2/semiconductor branched NWs.

Si or Si/SiO2 NWs with deposited Au-NPs were dispersed on SiO2 surface of heavily Si substrates as above and then immediately placed into the appropriate NW gas phase growth system to prepare branched semiconductor NWs. Ge branches were grown at 290 °C, 200 torr for 15 min, with the flow of 10 sccm GeH4 (10%), 10 sccm PH3 (1,000 ppm in H2), and 200 sccm H2 as described previously (41). The growth of other III–V and II–VI branches was achieved by thermal evaporation and vapor transport method (42). Powders with the same composition were put into the center of the quartz tube, which was heated to 650–780 °C, while the branch growth temperature was approximately 400–600 °C. 30 sccm of H2 was used as the carrier gas, and pressure was kept at 40 torr.

Device Fabrication and Measurement.

Single- and multiple-branch input devices were fabricated on SiO2 surface of Si substrates (50-nm thermal oxide, n-type 0.005 Ω-cm, Nova Electronic Materials) using electron beam lithography (43) followed by thermal evaporation of metals. Ti/Pd (5/50 nm) contacts were used for both Si and Ge NWs; Ti/Al/Pd/Au (20/80/20/30 nm) contacts were used for other III–V and II–VI semiconductor NWs. Current–voltage (I–V) data were recorded using an Agilent semiconductor parameter analyzer (Model 4156C) with contacts to devices made using a probe station (Desert Cryogenics, Model TTP4). EL from branched NW structures was characterized with a homebuilt microluminescence instrument (44). Arrays of Si/Au-NP NW devices were defined by photolithography (37). Ti/Pd (5/50 nm) metal contacts were deposited by thermal evaporation and then passivated by subsequent deposition of 50-nm thick Si3N4 coating (37). The completed device chip was subject to Au-branch growth as described above. The Au branches were modified in two steps. First, the devices were reacted with a 10 mg/mL solution of DMSO (Sigma-Aldrich) for approximately 4 h, followed by extensive rinsing with DMSO. Anti-PSA (AbI, clone ER-PR8, NeoMarkers) was then coupled to the succinimidyl(NHS)-terminated Au branches surfaces by reaction of 10–20 μg/mL antibody in a pH 8.4, 10 mM phosphate buffer solution for a period of 2–4 h. Unreacted NHS groups were subsequently passivated by reaction with ethanolamine under similar conditions. PSA and BSA protein samples in 1 μM phosphate buffer solution (pH, 7.4) were flowed under a flow rate of 0.30–0.60 mL/h through the microfluidic channel while monitoring the branch nanowire device properties as described in detail elsewhere (37).

Stress Field Simulation.

Stress field simulations were carried out using finite element method (ABAQUS software, version, 6.5-1). To simulate the stress in Si/GaAs branched structure, we took the axis of GaAs branch and Si backbone as 〈111〉 and 〈211〉, respectively, and the following material constants are used: modulus of elasticity, c11(GaAs) = 1.18 × 1011 Pa, c12(GaAs) = 0.538 × 1011 Pa, c44(GaAs) = 0.594 × 1011 Pa, c11(Si) = 1.662 × 1011 Pa,  , c44(Si) = 0.798 × 1011 Pa; lattice constant, a(Si) = 0.543 nm, a(GaAs) = 0.565 nm; backbone to branch width ratio, 2∶1.

, c44(Si) = 0.798 × 1011 Pa; lattice constant, a(Si) = 0.543 nm, a(GaAs) = 0.565 nm; backbone to branch width ratio, 2∶1.

Supplementary Material

Acknowledgments.

We thank Profs. R. Gordon and F. Spaepen and Drs. H. Yan, Y. Dong, J. Huang, Y. Wu, B. Timko, and Y. Fang for helpful discussions and constructive comments on the manuscript. C.M.L. acknowledges support of this work by the Air Force Office of Scientific Research and a National Security Science and Engineering Faculty Fellow award.

Footnotes

The authors declare no conflict of interest.

This article contains supporting information online at www.pnas.org/lookup/suppl/doi:10.1073/pnas.1108584108/-/DCSupplemental.

References

- 1.Hu J, Odom T, Lieber CM. Chemistry and physics in one dimension: Synthesis and properties of nanowires and nanotubes. Acc Chem Res. 1999;6:435–445. [Google Scholar]

- 2.Lieber CM. Nanoscale science and technology: Building a big future from small things. MRS Bull. 2003;28:486–491. [Google Scholar]

- 3.Li Y, Qian F, Xiang J, Lieber CM. Nanowire electronic and optoelectronic devices. Mater Today. 2006;9:18–27. [Google Scholar]

- 4.Law M, Goldberger J, Yang PD. Semiconductor nanowires and nanotubes. Annu Rev Mater Res. 2004;34:83–122. [Google Scholar]

- 5.Thelander C, et al. Nanowire-based one-dimensional electronics. Mater Today. 2006;9:28–35. [Google Scholar]

- 6.Wang ZL. Functional oxide nanobelts: Materials, properties and potential applications in nanosystems and biotechnology. Annu Rev Phys Chem. 2004;55:159–196. doi: 10.1146/annurev.physchem.55.091602.094416. [DOI] [PubMed] [Google Scholar]

- 7.Gudiksen MS, Lauhon LJ, Wang J, Smith DC, Lieber CM. Growth of nanowire superlattice structures for nanoscale photonics and electronics. Nature. 2002;415:617–620. doi: 10.1038/415617a. [DOI] [PubMed] [Google Scholar]

- 8.Wu Y, Fan R, Yang P. Block-by-block growth of single-crystalline Si/SiGe superlattice nanowires. Nano Lett. 2002;2:83–86. [Google Scholar]

- 9.Bjork MT, et al. One-dimensional heterostructures in semiconductor nanowhiskers. Appl Phys Lett. 2002;80:1058–1060. [Google Scholar]

- 10.Lauhon LJ, Gudiksen MS, Wang D, Lieber CM. Epitaxial core-shell and core-multi-shell nanowire heterostructures. Nature. 2002;420:57–61. doi: 10.1038/nature01141. [DOI] [PubMed] [Google Scholar]

- 11.Tian B, Xie P, Kempa TJ, Bell DC, Lieber CM. Single crystalline kinked semiconductor nanowire superstructures. Nat Nanotechnol. 2009;4:824–829. doi: 10.1038/nnano.2009.304. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 12.Dick KA, et al. Synthesis of branched ‘nanotrees’ by controlled seeding of multiple branching events. Nat Mater. 2004;3:380–384. doi: 10.1038/nmat1133. [DOI] [PubMed] [Google Scholar]

- 13.Wang D, Qian F, Yang C, Zhong ZH, Lieber CM. Rational growth of branched and hyperbranched nanowire structures. Nano Lett. 2004;4:871–874. [Google Scholar]

- 14.Gao P, Wang ZL. Self-assembled nanowire-nanoribbon junction arrays of ZnO. J Phys Chem B. 2002;106:12653–12658. [Google Scholar]

- 15.Yan HQ, He RR, Pham J, Yang PD. Morphogenesis of one-dimensional ZnO nano- and microcrystals. Adv Mater. 2003;15:402–405. [Google Scholar]

- 16.Zhou J, et al. Three-dimensional tungsten oxide nanowire networks. Adv Mater. 2005;17:2107–2110. [Google Scholar]

- 17.Bierman MJ, Lau YKA, Kvit AV, Schmitt AL, Jin S. Dislocation-driven nanowire growth and Eshelby Twist. Science. 2008;320:1060–1063. doi: 10.1126/science.1157131. [DOI] [PubMed] [Google Scholar]

- 18.Zhu J, et al. Formation of chiral branched nanowires by the Eshelby Twist. Nat Nanotechnol. 2008;3:477–481. doi: 10.1038/nnano.2008.179. [DOI] [PubMed] [Google Scholar]

- 19.Dong A, Tang R, Buhro WE. Solution-based growth and structural characterization of homo- and heterobranched semiconductor nanowires. J Am Chem Soc. 2007;129:12254–12262. doi: 10.1021/ja0737772. [DOI] [PubMed] [Google Scholar]

- 20.Jung Y, Ko DK, Agarwal R. Synthesis and structural characterization of single-crystalline branched nanowire heterostructures. Nano Lett. 2007;7:264–268. doi: 10.1021/nl0621847. [DOI] [PubMed] [Google Scholar]

- 21.Zhou W, et al. Controllable fabrication of high-quality 6-fold symmetry-branched CdS nanostructures with ZnS nanowires as templates. J Phys Chem C. 2008;112:9253–9260. [Google Scholar]

- 22.Milliron DJ, et al. Colloidal nanocrystal heterostructures with linear and branched topology. Nature. 2004;430:190–195. doi: 10.1038/nature02695. [DOI] [PubMed] [Google Scholar]

- 23.Dick KA, et al. Position-controlled interconnected InAs nanowire networks. Nano Lett. 2006;6:2842–2847. doi: 10.1021/nl062035o. [DOI] [PubMed] [Google Scholar]

- 24.Suyatin DB, et al. Electrical properties of self-assembled branched InAs nanowire junctions. Nano Lett. 2008;8:1100–1104. doi: 10.1021/nl073193y. [DOI] [PubMed] [Google Scholar]

- 25.Gautam UK, Fang X, Bando Y, Zhan J, Golberg D. Synthesis, structure, and multiply enhanced field-emission properties of branched ZnS nanotube-In nanowire core-shell heterostructures. ACS Nano. 2008;2:1015–1021. doi: 10.1021/nn800013b. [DOI] [PubMed] [Google Scholar]

- 26.Meng G, et al. A general synthetic approach to interconnected nanowire/nanotube and nanotube/nanowire/nanotube heterojunctions with branched topology. Angew Chem Int Ed Eng. 2009;48:7166–7170. doi: 10.1002/anie.200901999. [DOI] [PubMed] [Google Scholar]

- 27.Chen B, et al. Crystalline silicon nanotubes and their connections with gold nanowires in both linear and branched topologies. ACS Nano. 2010;4:7105–7112. doi: 10.1021/nn102689z. [DOI] [PubMed] [Google Scholar]

- 28.Jun K, Jacobson JM. Programmable growth of branched silicon nanowires using a focused ion beam. Nano Lett. 2010;10:2777–2782. doi: 10.1021/nl100662z. [DOI] [PubMed] [Google Scholar]

- 29.Johnson CJ, Dujardin E, Davis SA, Murphy CJ, Mann S. Growth and form of gold nanorods prepared by seed-mediated, surfactant-directed synthesis. J Mater Chem. 2002;12:1765–1770. [Google Scholar]

- 30.Morales AM, Lieber CM. A laser ablation method for the synthesis of crystalline semiconductor nanowires. Science. 1998;279:208–211. doi: 10.1126/science.279.5348.208. [DOI] [PubMed] [Google Scholar]

- 31.Sze SM. Physics of Semiconductor Devices. New York: Wiley; 1981. [Google Scholar]

- 32.Hausmann DM, Kim E, Becker J, Gordon RG. Atomic layer deposition of hafnium and zirconium oxides using metal amide precursors. Chem Mater. 2002;14:4350–4358. [Google Scholar]

- 33.Mzhari B, Morkoc H. Surface recombinationin GaAs PN junction diode. J Appl Phys. 1993;73:7509. [Google Scholar]

- 34.Huang Y, Duan X, Lieber CM. Nanowires for integrated multicolor nanophotonics. Small. 2005;1:142–147. doi: 10.1002/smll.200400030. [DOI] [PubMed] [Google Scholar]

- 35.Huang Y, et al. Logic gates and computation from assembled nanowire building blocks. Science. 2001;294:1313–1317. doi: 10.1126/science.1066192. [DOI] [PubMed] [Google Scholar]

- 36.Cui Y, Wei Q, Park H, Lieber CM. Nanowire nanosensors for highly sensitive and selective detection of biological and chemical species. Science. 2001;293:1289–1292. doi: 10.1126/science.1062711. [DOI] [PubMed] [Google Scholar]

- 37.Zheng G, Patolsky F, Cui Y, Wang WU, Lieber CM. Multiplexed electrical detection of cancer markers with nanowire sensor arrays. Nat Biotechnol. 2005;23:1294–1301. doi: 10.1038/nbt1138. [DOI] [PubMed] [Google Scholar]

- 38.Patolsky F, Lieber CM. Nanowire nanosensors. Mater Today. 2005;8:20–28. [Google Scholar]

- 39.Wu Y, et al. Controlled growth and structures of molecular-scale silicon nanowires. Nano Lett. 2004;4:433–436. [Google Scholar]

- 40.Sun XH, et al. Surface reactivity of Si nanowires. J Appl Phys. 2001;89:6396–6399. [Google Scholar]

- 41.Greytak AB, Lauhon LJ, Gudiksen MS, Lieber CM. Growth and transport properties of complementary germanium nanowire field-effect transistors. Appl Phys Lett. 2004;84:4176–4178. [Google Scholar]

- 42.Jiang X, et al. “InAs/InP radial nanowire heterostructures as high electron mobility devices”. Nano Lett. 2007;7:3214–3218. doi: 10.1021/nl072024a. [DOI] [PubMed] [Google Scholar]

- 43.Cui Y, Zhong Z, Wang D, Wang WU, Lieber CM. High performance silicon nanowire field effect transistors. Nano Lett. 2003;3:149–152. [Google Scholar]

- 44.Qian F, Gradecak S, Li Y, Wen Y, Lieber CM. Core/multishell nanowire heterostructures as multicolor, high-efficiency light-emitting diodes. Nano Lett. 2005;5:2287–2291. doi: 10.1021/nl051689e. [DOI] [PubMed] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.