Abstract

Paper is the ideal substrate for the development of flexible and environmentally sustainable ubiquitous electronic systems, which, combined with two-dimensional materials, could be exploited in many Internet-of-Things applications, ranging from wearable electronics to smart packaging. Here we report high-performance MoS2 field-effect transistors on paper fabricated with a “channel array” approach, combining the advantages of two large-area techniques: chemical vapor deposition and inkjet-printing. The first allows the pre-deposition of a pattern of MoS2; the second, the printing of dielectric layers, contacts, and connections to complete transistors and circuits fabrication. Average ION/IOFF of 8 × 103 (up to 5 × 104) and mobility of 5.5 cm2 V−1 s−1 (up to 26 cm2 V−1 s−1) are obtained. Fully functional integrated circuits of digital and analog building blocks, such as logic gates and current mirrors, are demonstrated, highlighting the potential of this approach for ubiquitous electronics on paper.

Subject terms: Electrical and electronic engineering, Two-dimensional materials, Electronic devices

Paper is a promising substrate for flexible and environmentally sustainable electronic devices. Here, the authors combine chemical vapor deposition of MoS2 with inkjet printing of a hexagonal boron nitride (hBN) dielectric and silver electrodes, to fabricate flexible MoS2 field-effect transistors on paper, and then combine the latter with printed graphene resistors and silver interconnects to create inverters, logic gates and current mirrors.

Introduction

In recent years, electronics has witnessed impressive technological achievements, owing to the development of new processes and materials with extraordinary electrical and mechanical properties, which have enabled the development of Internet of Things applications, ranging from wearable electronics to mobile healthcare. This has led to a continuous and marked increase in demand of light-weight, flexible, and low-cost devices, posing strong constrains on traditional fabrication methods1,2. In addition, this type of pervasive and versatile electronics had led to further concerns on sustainability, such as the treatment of waste at the end of the product life-cycle. Derived from abundant and renewable raw materials, paper-based consumer electronics is expected to alleviate landfill and environmental problems and to reduce the impact associated with recycling operations, whilst offering cost-effectiveness and large flexibility3. Despite the fact that several devices and applications have been reported in the literature4, paper is still a challenging substrate for electronics, rarely employed without the addition of coating/laminating layers5,6. Its porous structure (which in turn leads to high roughness), limited stability and durability (mainly due poor thermal and humidity resistance), and high hygroscopicity (which can influence the electrical characterization of devices fabricated on top of it), combined with the lack of winning reliable fabrication techniques, is preventing its exploitation at the industrial level7,8.

Two-dimensional materials (2DMs) combine good tunable electronic properties with high mechanical flexibility, making them extremely promising as building blocks for flexible electronics9,10. Moreover, they can be easily produced in solution with mass scalable and low-cost techniques, such as liquid-phase exfoliation11, enabling their deposition by simple fabrication techniques such as inkjet printing12–17. 2D semiconducting materials, such as transition metal dichalcogenides (TMDCs)18,19, with extended bandgap tunability through composition, thickness, and possibly even strain control, represent promising materials as channels for field-effect transistors (FETs), which are fundamental components in electronics. However, up to now, fully printed TMDC-based transistors have demonstrated limited performance, showing mobility of the order of under 0.5 cm2 V−1 s−1 and ION/IOFF ratios of hundreds, using liquid electrolytes as insulating layers20,21. Among the various TMDCs, molybdenum disulfide (MoS2) has been widely studied, owing to its outstanding electrical and optical properties22–26. Lin et al. 27 reported FETs made with solution-processed MoS2, showing remarkable performance (average mobility of ~7–11 cm2 V−1 s−1), but device fabrication required acid cleaning and annealing above 200 °C, which are incompatible with substrates such as paper. A large mobility of 19 cm2 V−1 s−1 for a MoS2/graphene transistor was reported in ref. 28: graphene allows increasing carrier mobility, but this negatively affects the ION/IOFF ratio.

We combine chemical vapor deposition (CVD), for the growth of high-quality MoS2 channels, with inkjet printing29,30, which allows to design and fabricate customizable devices and circuits exploiting 2DMs-based inks, whose capability to be printed on top of CVD-grown materials has been successfully demonstrated in ref. 16. In this work, an application-specific integrated circuit design approach, known as “channel array”, is proposed: this is based on the transfer of strips of CVD-grown MoS2, onto paper substrate where the rest of the devices and circuits, source and drain contacts (which define the effective channel length and width), gate dielectric, gate contacts, and connections, are fully customized exploiting inkjet printing technique, giving a degree of freedom to the designer. This method allows to keep the flexibility and versatility of an all-inkjet technology, with the difference that here a high-quality channel is already placed on the substrate, by taking advantage of the CVD-grown TMDC. Moreover, as both methods are compatible with large-area fabrication processes, their combination could open a possible exploitation at the industrial level.

The MoS2 FETs fabricated with the channel array method operate at supply voltage below 2 V, with remarkable transistor performance, such as an average field-effect mobility of 5.5 cm2 V−1 s−1 (with best performance reaching 26 cm2 V−1 s−1), negligible leakage currents (smaller than 5 nA), and an average ION/IOFF ratio of 8 × 103 (up to 5 × 104). We further exploit the possibility to produce high-performance transistors with the channel array method by demonstrating more complex circuits, such as logic gates (such as NOT and NAND) and analog circuits. This paves the way towards the introduction of the channel array approach in all applications where flexible and/or disposable electronics is required.

Results

Fabrication of MoS2 FETs on paper

The rationale of our approach is the combination of two fabrication techniques, which up to now have been used for very different applications, to have high-quality semiconducting substrates easily customizable to obtain devices and circuits with a versatile printing technique. The advantage of inkjet-printing is the fast prototyping, which allows for on-the-fly corrections as well as easy pattern changes, simplifying the manufacturing process. Moreover, being an additive and mask-less method, it also cuts down materials and energy consumption, reducing the number of processing steps, time, space, and waste production during the fabrication. On the other hand, inkjet-printing presents critical aspects, such as the need to use inks with specific rheological properties, and, more importantly, the current lack of semiconducting 2DM-based inks for high-performance FETs. Even if expensive, lacking in compatibility with arbitrary substrates, suffering from atomic vacancies and batch-to-batch variations, CVD is, so far, the most-promising bottom–up approach to obtain high-quality semiconducting layer and may become the method of choice, also considering the recent progress in the CVD growth of MoS2 involving a low-cost, large-area roll-to-roll approach31.

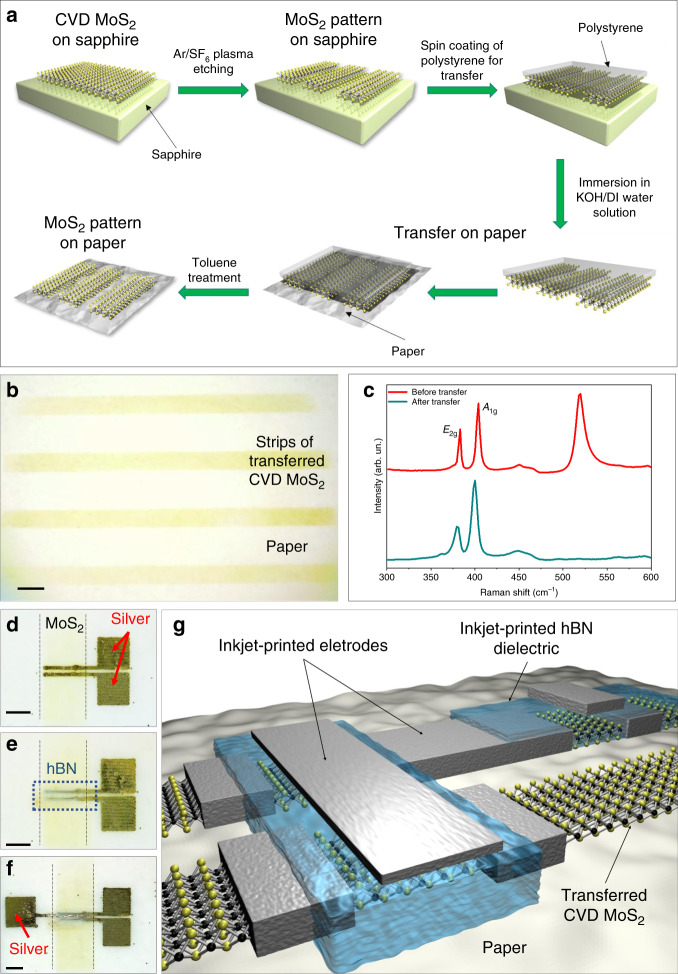

Figure 1a illustrates the procedure followed to pattern CVD MoS2 and its transfer to paper substrate (a detailed description of the process is reported in Methods, an alternative method for CVD growth and transfer is presented in Supplementary Note 1). After the transfer, the polystyrene carrier film is dissolved in toluene, resulting in MoS2 strips on paper, as shown in Fig. 1b (an atomic force microscopy micrograph of the MoS2 film on the sapphire substrate before the transfer is reported in Supplementary Note 2).

Fig. 1. Transferring scheme of MoS2 channel stripes and fabrication process of MoS2 FETs.

a Schematic representation of the patterning and transferring procedure employed to obtain MoS2 strips on paper. b Optical micrograph showing the transferred MoS2 strips on paper. The scale bar corresponds to 1 mm. c Raman spectra acquired on the as-grown MoS2 layer on rigid substrate (red line) and after MoS2 transfer to paper (cyan line). d–f Fabrication steps of the inkjet-printed transistors on paper: d Inkjet-printing of silver source and drain contacts. e Inkjet-printing of the hBN dielectric layer (defined by the blue-dotted frame). f Inkjet printing of silver top-gate contact. The scale bars in d–f correspond to 250 μm. g Sketch showing an inkjet-printed circuit on paper with CVD-grown MoS2 channel.

To evaluate the crystalline quality of the MoS2 before and after the transfer process from the rigid substrate to the paper, Raman spectroscopy is employed. Figure 1c shows the Raman spectra before (red line) and after (cyan line) the transfer. The red spectrum presents the E2g and A1g modes at 383 cm−1 and at 403 cm−1 of single-layer MoS2, representative of the in-plane and out-of-plane vibrations of S–Mo–S, respectively32. After the transfer process, the MoS2 Raman modes appear slightly shifted and broadened, i.e., the E2g and A1g modes peak at 380 cm−1 and at 400 cm−1, respectively. As previously reported in ref. 33, the softening of Raman modes can be attributed to uniaxial strain, albeit the E2g mode should suffer a larger shift compared with the A1g mode. In our case, the softening of the Raman modes is comparable, ruling out any strain effect on the MoS2. Therefore, we argue that the softening is mainly owing to heating effects related to the poor heat dissipation of the paper substrate. This hypothesis is also supported by the broadening of the full-width-at-half-maximum (FWHM) of both modes. Indeed, the E2g FWHM increases from ~3 cm−1, before transfer, up to ~7 cm−1 after the transfer process. In the case of the A1g mode, the broadening is less evident, with the FWHM increasing from ~4 cm−1 up to ~6 cm−1.

Figure 1d–f show the fabrication of inkjet-printed MoS2 FETs on paper. First, the source and drain contacts are printed on a MoS2 stripe to define the channel area of the transistor (Fig. 1d). Second, a hexagonal boron nitride (hBN) film is printed on the MoS2 channel (Fig. 1e). This 2D insulating material is chosen because of its notable dielectric properties and negligible leakage current15,20,34,35. Finally, a top-gate electrode is printed on top of hBN (Fig. 1f). Either silver or graphene inks have been used to print the source and drain contacts as well as the top-gate contacts. The FETs are then connected to each other using the routes defined between the MoS2 strips, to create the integrated circuit in an efficient and versatile way. This approach is qualitatively described in Fig. 1g.

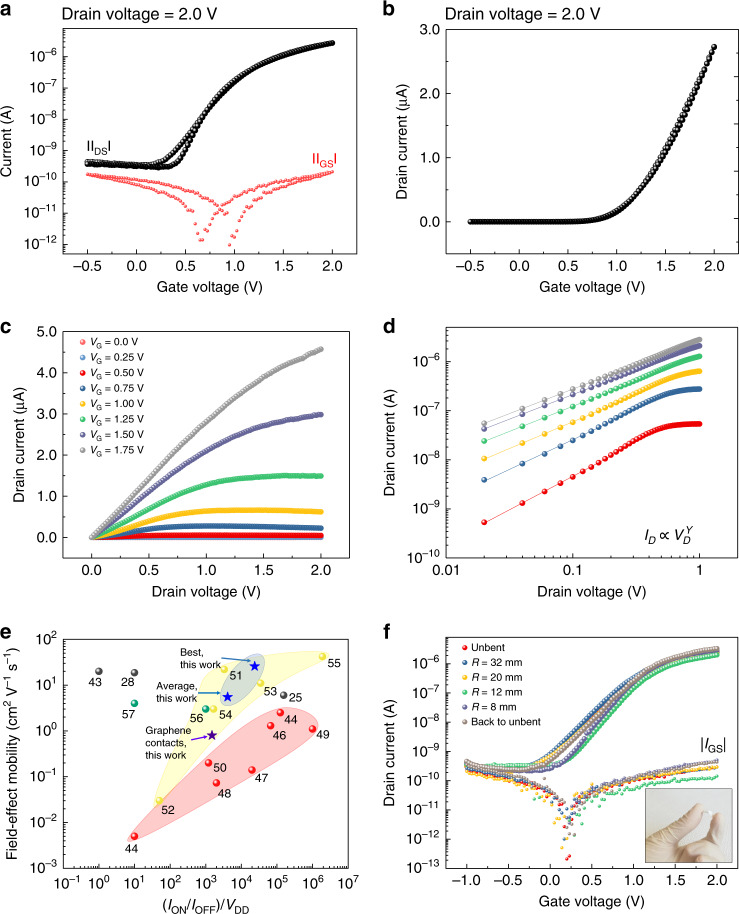

Electrical characterization of MoS2 FETs

At first, a commercial silver ink (see Methods) was chosen to print the electrodes, because it can assure very high conductivity with just one printing pass, and it has shown ohmic contact with MoS229. Typical transfer and output characteristics of the MoS2 FETs are reported in Fig. 2a, c. The devices work in the enhancement mode, can operate at low supply voltage (<2 V), and exhibit a threshold voltage (VTH) in the range of ±1 V (see Supplementary Fig. 7c and Supplementary Fig. 7e). As can be seen, the leakage current IGS (red dots, Fig. 2a) through the insulator is negligible as compared to the drain current IDS (black dots, logarithmic scale, Fig. 2a; black dots, linear scale, Fig. 2b), further confirming the good insulating properties of the inkjet-printed hBN film. The saturation regime is reached for low drain-to-source voltage (VDS), i.e., VDS < 2 V. Almost negligible contact resistance is shown from the output characteristic. Indeed, as can be seen from the log–log plot (Fig. 2d), the linearity parameter γ, describing the relation , is found to be 1.1 on average, indicating a good contact between the CVD MoS2 and the inkjet-printed silver electrodes.

Fig. 2. Electrical characterization of the MoS2 FETs with inkjet-printed silver contacts in ambient conditions.

a Typical transfer characteristic curve measured as a function of the gate voltage for a drain voltage of 2.0 V. Logarithmic scale: black dots, drain current; red dots, gate current. b Typical transfer characteristic curve measured as a function of the gate voltage for a drain voltage of 2.0 V in linear scale. c Typical output characteristic measured at different gate voltages (from VGS = 0.0 V to VGS = 1.75 V, steps of 0.25 V). d Log–log curves of the output characteristic in low drain voltage region. Ohmic behavior is observed, suggesting good electrical contact between the silver contacts and MoS2. e Field-effect mobility and (ION/IOFF)/VDD for FETs characterized on paper substrates previously reported in the literature. VDD is the supply voltage for each device. Blue stars, this work, inkjet-printed silver contacts; purple star, this work, inkjet-printed graphene contacts; black dots, 2D materials (25, 28, 43); red dots, organic semiconductors (44, 45, 46, 47, 48, 49, 50); yellow dots, inorganic oxides (51, 52, 53, 54, 55); green dots, CNTs (56, 57). f Transfer characteristics and gate leakage currents measured for different bending radii along the current direction for a drain voltage of 2 V; inset, picture of a sample with MoS2 FET fabricated on paper.

Charge carrier field-effect mobility (µFE) is one of the most important figures of merit defining the quality of transistor electrical performance. It can be extrapolated using the classical model for devices operating in the saturation regime (VDS > VGS − VTH):

| 1 |

where Ci is the capacitance of the insulator per unit area, W and L are the transistor channel width and length, respectively, and VGS is the gate voltage. As suggested in ref. 8, in order to avoid any mobility overestimation, the capacitance was measured under quasi-static conditions (details about the quasi-static capacitance measurement and setup are reported in Supplementary Note 3). To this purpose, parallel plate capacitor structures, in which hBN is sandwiched between silver bottom/top electrodes were fabricated and tested (see Methods). The extracted average value of 230 nF cm2 is in line with other quasi-static measurement performed on both organic and hybrid materials8,36–38. Thanks to the high capacitive coupling, which results in an enhanced polarization and leads to a high number of carriers at the insulator-semiconductor interface, the devices show an average charge carrier mobility of 5.5 cm2 V−1 s−1 and ION/IOFF ratio of 8 × 103. ION is computed for IDS extracted for gate voltage VGS = VGSoff + VDD and drain voltage VDS = VDD, where VDD is the supply voltage, and VGSoff is the gate voltage for the lowest current flowing in the device, i.e., the OFF current IOFF39. The detailed electrical characterization is reported in Supplementary Figs. 2 and 3. Remarkably, this mobility value is comparable to already reported CVD-grown MoS2 transistors fabricated on rigid substrates using standard microelectronic fabrication techniques40–42, confirming that our methodology, based on the channel array, allows to use inkjet-printing for the fabrication of the devices, without affecting the electronic properties of the channel.

Figure 2e shows µFE and the normalized ION/IOFF ratio for our devices compared with those previously reported in the literature: the closer the points to the top-right corner, the better the performance. We considered only transistors fully fabricated on paper or transferred on paper after fabrication. For a fair comparison, all the ION/IOFF values are re-calculated considering the International Technology Roadmap for Semiconductors definition39, and then divided by the respective supply voltage VDD. This normalization allows to take into account the operating voltage ranges of the considered FETs, which is a crucial problem for portable applications, where low power consumption is often required. They have been divided into four groups according to the nature of the semiconductor used as channel: 2D materials25,28,43 organic semiconductors44–50, inorganic oxide semiconductors51–55, carbon nanotubes56,57. Our devices show competitive electrical performance and are the only one, where both the contacts and the insulating layers are deposited by means of inkjet printing (for a detailed comparison see Supplementary Data 1). While maintaining a high ION/IOFF ratio, the mobility values extracted from the MoS2 FETs are larger than those obtained for organic semiconductors. Transistors that show comparable or better performance than those presented in this work, as reported in refs. 25,51,53,55, were fabricated using micro-fabrication techniques for the deposition of insulator and contact layers, as well. It is worth mentioning, that the mobility extracted in this work is comparable to the one found for CVD MoS2 FETs entirely fabricated using conventional microelectronic techniques on planarized paper substrates25. Note that the type of paper used in the literature may be different, and this may affect the performance of the devices and the reproducibility, hence comparison should be done carefully. In some cases, planarization layers were introduced to mitigate the surface roughness of the paper substrates and high-temperature processes were employed, thus increasing the complexity of the transistor manufacturing. In our work, the fabrication process and the electrical characterization are carried out at ambient condition on a commercially available paper, designed for printed electronics (see Supplementary Note 6) that cannot withstand temperatures over 120 °C. The potentiality of our approach stands in the coherent combination of two large-area fabrication processes in order to obtain good electrical performances. In Supplementary Note 5 and Supplementary Data 2, a comparison with devices fabricated on flexible substrates (other than paper) is reported. As can be seen, our devices are comparable with the best-in-class presented devices.

In order to confirm the compatibility of our technology with flexible substrates, the electromechanical properties of the devices are investigated for various bending radii (R) (more details can be found in Supplementary Note 4.1). Figure 2f shows transfer characteristics recorded for R values of 32, 20, 12, and 8 mm. No relevant changes both in the drain and the gate currents are observed, indicating that the device electrical performance is not affected under the applied strain conditions.

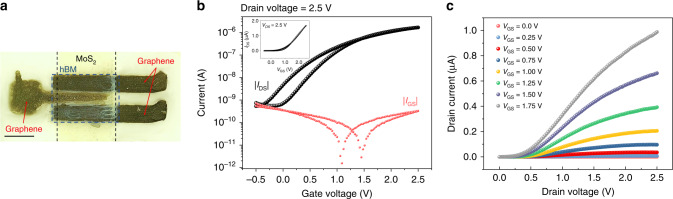

We have then focused on the fabrication of fully 2D-material-based transistors with inkjet-printed graphene source, drain, and gate contacts (see Methods). An optical micrograph of a fully 2D-material-based FET is shown in Fig. 3a, whereas Fig. 3b, c report typical transfer and output characteristic, respectively. These transistors show a reduced effective μFE (~0.8 cm2 V−1 s−1), and an ION/IOFF ratio about one order of magnitude smaller (~3 × 103), compared with transistors with silver contacts (Fig. 2e). The reduced performance is likely related to the formation of Schottky contacts, which in turn increases the contact resistance, as evident from Fig. 3c, where non-linear behavior of the output characteristic can be observed for small VDS. However, it is remarkable that the extracted field-effect mobility is only six times smaller than the one obtained for a thin film transistor with exfoliated MoS2 channel and CVD‐grown graphene source/drain electrodes (4.5 cm2 V−1 s−1)58.

Fig. 3. Optical image and electrical characterization of a fully 2D-material-based FETs.

a Optical micrograph of a fully 2D-material-based transistor on paper. The scale bar corresponds to 250 μm. b Typical transfer characteristic curve measured as a function of the gate voltage for a drain voltage of 2.5 V. Logarithmic scale: black dots, drain current; red dots, gate current. inset, Typical transfer characteristic curve measured as a function of the gate voltage for a drain voltage of 2.5 V in linear scale. c Typical output characteristic curves measured at increasing gate voltages (from VGS = 0.0 V to VGS = 1.75 V, steps of 0.25 V).

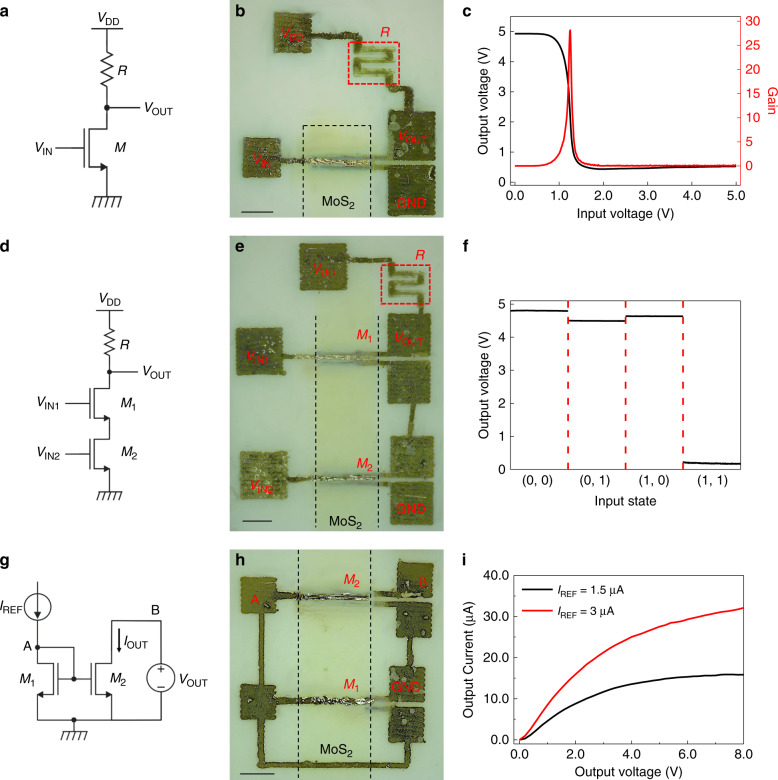

Integrated circuits on paper

To demonstrate the potential of the fabricated FETs as building blocks for integrated circuits exploiting the channel array technology, different types of circuits have been designed and fabricated. MoS2 FETs with inkjet-printed silver contacts were selected owing to the high ION/IOFF ratio, intrinsic gain, and low power supply voltage to fabricate a resistor-transistor logic (RTL) inverter, consisting of a transistor and an inkjet-printed graphene resistor. Figure 4a, b show the schematic and the optical image of a RTL inverter, respectively. The transfer characteristic of an inverter is shown in Fig. 4c (left axis), together with the gain G (right axis), defined as the slope dVOUT/dVIN of the transfer curve (where VIN and VOUT are the input and output voltages, respectively). The inverter exhibits a high-gain value, close to 30 under a voltage bias of 5 V, in agreement with previously reported inverters based on CVD-grown MoS2 fabricated on rigid substrates41,59.

Fig. 4. Logic gates and current mirror based on inkjet-printed MoS2 FETs.

a Electrical schematic and b optical image of an inverter. c Output voltage (left axis) and voltage gain (right axis) of the inverter gate as a function of the input voltage. d Electrical schematic and e optical image of a NAND gate. f Output voltage of the NAND gate as a function of the input states (VIN1, VIN2). Voltage bias is 5 V for both the inverter and the NAND gate. g Electrical schematic and h optical image of a current mirror. i Output current of the current mirror as a function of the output voltage for two different values of the reference current. Legend: VDD, supply voltage; GDN, ground reference; VIN and VOUT, input and output voltage; M, inkjet-printed transistor. R, inkjet-printed graphene resistor. The scale bars in b, e, h correspond to 250 μm.

The schematic and the optical image of a NAND gate are shown in Fig. 4d, e, whereas Fig. 4f shows the output voltage of the circuit as a function of the inputs (VIN1,VIN2). The low and high logic values of the inputs correspond to voltages of 0 V and 5 V, respectively. The output voltage is high (i.e., at logic state “1”) when at least one input is in the logic state “0”, and therefore at least one transistor is in the OFF state. The output voltage is low (i.e., at logic state “0”) only when both inputs are at the logic state “1”: in these conditions both transistors are in the ON state. The possibility to implement NAND gates is particularly important, as all other logic functions can be implemented using NAND gates.

As a further demonstration of the potential of the presented technology, we propose an application for analog electronics. Current mirrors are fundamental building blocks in analog electronic circuits, where they are widely used for operational amplifiers, bandgap voltage reference, etc.60, and they can also be exploited in neural networks, in order to implement matrix-vector multiplication61. Figure 4g, h show the schematic and the optical image of the fabricated current mirror. The output transistor (M2) is 10 times wider than the input transistor (M1), whereas all the other transistor parameters are identical; therefore, the current mirror has a nominal gain of 10. Figure 4i shows the current mirror output characteristic, i.e., the output current as a function of the output voltage, for two different values of the input reference current. As shown in the plot, for sufficiently high output voltages (i.e., M2 in saturation) the output current is about 10 times larger than the reference current (IREF), in accordance with the circuit design.

Discussion

We have successfully demonstrated high-performance MoS2-based transistors that combine the numerous advantages of using paper as a substrate with the versatility of inkjet-printing technique, whilst maintaining the good electrical properties of CVD-grown MoS2. A maximum field-effect mobility of 26 cm2 V−1 s−1 and an ION/IOFF ratio of up to 5 × 104 were achieved. Bending tests have shown that the device electrical properties are robust under applied strain (up to a bending radius of 8 mm). Moreover, our device fabrication approach has been proven to be suitable for the development of complete integrated circuits, such as high-gain inverters, logic gates, and current mirrors. This work demonstrates the great potential of the channel array technology for next-generation electronics on paper, ranging from analogic to digital circuits for cost-efficient and practical applications.

Methods

Materials

PEL P60 (purchased from Printed Electronics Limited) is used as paper substrate (more details can be found in Supplementary Note 6). A commercial silver ink (Sigma-Aldrich) is used to print the metal contacts. Bulk graphite (purchased from Graphexel or Sigma-Aldrich, 99.5% grade) and bulk boron nitride (purchased from Sigma-Aldrich, >1 μm, 98% grade) powders were used to prepare the 2DMs inks. The bulk powders are dispersed in deionized water (resistivity 18.2 MΩ cm−1) at a concentration of 3 mg mL−1 and 1-pyrenesulphonic acid sodium salt (PS1, purchased from Sigma-Aldrich), purity ≥97%, is added at a concentration of 1 mg mL−1. The graphite and boron nitride dispersions are then sonicated for 72 h and 120 h, respectively, using a 300 W Hilsonic HS 1900/Hilsonic FMG 600 bath sonicator at 20 °C. The resultant dispersions is centrifuged at 3500 rpm (g factor = 903) for 20 minutes at 20 °C using a Sigma 1–14 K refrigerated centrifuge in order to separate out and discard the residual bulk, non-exfoliated flakes. The remaining supernatant, now containing the correct flake size and monolayer percentage, is centrifuged twice to remove excess PS1 from the dispersion. After washing, the precipitate is re-dispersed in the printing solvent, made as described in ref. 16. The concentration of the resultant inks are assessed using a Varian Cary 5000 UV-Vis spectrometer and the Lambert-Beer law, with extinction coefficients of 2460 (at 660 nm) and 1000 L g−1 m−1 (at 550 nm) for graphene11 and hBN62, respectively. Full characterization of the material (lateral size and thickness distribution, crystallinity, etc.) has been presented in refs. 16,34,63.

Growth of MoS2 and transfer on paper

Single- and few-layer MoS2 have been grown by CVD on c-plane sapphire64. CVD growth is performed at atmospheric pressure using ultra-high-purity Ar as the carrier gas. The substrates are placed face-down 15 mm above a crucible containing ∼3 mg of MoO3 (99.998% Alfa Aesar) and loaded into a split-tube two-zone CVD furnace with a 30 mm outer diameter quartz tube. A second crucible containing 1 g of sulfur (99.9% purity, Sigma-Aldrich) is loaded upstream from the growth substrates and heated to 140 °C. Just before starting the growth, the tube is flushed with Ar at room temperature and atmospheric pressure. The furnace is pre-heated to 750 °C for few hours for temperature stabilization. The substrate and MoO3 precursor were then loaded into the growth area of the furnace to start the growth. Ar is supplied with a flow of 10 sscm. After 10 min growth at 750 °C, the furnace is left to cool naturally. The synthesized MoS2 film is transferred from the native sapphire substrate to the paper substrates65. Prior to the film transfer, MoS2 is patterned to obtain a stripped structure on the growth substrate. The pattern is defined by means of Ar/SF6 plasma etching in an Oxford Cobra Reactive Ion Etching system. The etch mask is created by optical lithography using AZ 5214E photoresist. A 5% KOH solution in DI water is employed to remove the etch mask. The sample is then rinsed in DI water for several times to remove the KOH remnants. To transfer the patterned film, the sapphire substrate with the MoS2 layer film is first covered with a polystyrene film by spin coating a solution of polystyrene in toluene onto the substrate, which is then immersed in DI water. To facilitate the lift-off process, a solution of KOH in DI water is also added for a short time. After that, the carrier polystyrene film with the MoS2 layer is rinsed for several times in DI water. To remove the absorbed water the polymeric film is dried at 50 °C in dry air atmosphere and then transferred onto the paper substrate. To improve the adhesion between the carrier polymer film and the wafer the sample is baked at 150 °C for about an hour. The polystyrene carrier film is then dissolved in toluene resulting in a MoS2 film on paper. Raman characterization before and after transfer has been performed with a Renishaw InVia spectrometer equipped with a confocal optical microscope and a 532 nm excitation laser. The spectral resolution of the system is 1 cm−1. Raman experiments were carried out employing a ×50 objective (N.A. 0.6), laser power of 5 mW and an acquisition time of 2 s. The pixel size is 1 µm × 1 µm.

Devices fabrication

MoS2 transistors are fabricated in a top-gate/top-contact configuration on the CVD MoS2 stripes transferred on paper. A Dimatix Materials Printer 2850 (Fujifilm) is used to define the contacts and the insulator layers under ambient conditions. It is worth underlining that no annealing or post-treatment process is performed after any printing step. The silver ink is deposited with a single printing pass using one nozzle, a drop spacing of 40 μm, and keeping the printer platen at room temperature. Cartridges with a typical droplet volume of 1 pL are used for the definition of the contacts. When the 2.5 mg ml−1 graphene ink is employed, source and drain contacts are inkjet-printed using a drop spacing of 20 μm, and 20 printing passes. Cartridges with a droplet volume of 10 pL are used for the definition of the graphene contacts. For the top-gate contacts, only six printing passes of graphene ink at the same concentration are used in order to reduce the possibility of overlapping with the source and drain contacts (which would significantly increase the leakage current) at each print pass. A ~2 mg/mL hBN ink is printed on top of the CVD-grown MoS2 using a drop spacing of 20 μm and 80 printing passes. Cartridges with a droplet volume of 10 pL are used for the definition of the insulating layer. Several transistors have been fabricated (with a yield of around 80%) and characterized with a nominal width of ~500 μm and length varying between 40 μm and 60 μm (further details can be found Supplementary Table 1).

Parallel plate capacitors with silver/graphene bottom/top electrodes are also printed on paper to evaluate the capacitance of the hBN layers. The inks and the fabrication procedures are kept the same for all the reported devices.

Electrical characterization

All the electrical measurements are performed under ambient conditions. The transistor characterization is carried out using a Keithley SCS4200 parameter analyzer. Capacitance measurements are performed with an R&SRTO2014 oscilloscope and a HP 33120A function/arbitrary waveform generator. The detailed description of the measurement setup can be found in the Supplementary Information.

Supplementary information

Descriptions of Additional Supplementary Files

Acknowledgements

We acknowledge the ERC PEP2D (contract no. 770047) and H2020 WASP (contract no. 825213) for financial support. C.Ca., C.Co., G.F.,T.M. acknowledge the Graphene Flagship Core 3 (contract no. 881603). R.W. acknowledges the Hewlett-Packard Company for financial support in the framework of the Graphene NOWNANO Centre for Doctoral Training;. C.Ca. acknowledges useful discussions with Alessandro Molle, and financial support from the Grand Challenge EPSRC grant EP/N010345/1. S.P. and C.Co acknowledge financial support from Compagnia di San Paolo (project STRATOS).

Author contributions

R.W., S.M. developed the inks under the supervision of C.Ca.; D.K.P., M.P., S.P., D.H.K., and F.F. carried out the MoS2 growth and the transfer on the paper substrates, and performed the Raman spectroscopy and imaging under the supervision of T.M and C.Co.; S.C., L.P., G.C., and G.F. fabricated the electronic devices, performed the electrical measurements, and analyzed the results; G.F, G.I., and M.M. designed and supervised the research. All authors discussed the results and contributed to the manuscript.

Data availability

The data that support the findings of this work are available from the corresponding authors upon reasonable request.

Competing interests

The authors declare no competing interests.

Footnotes

Peer review information Nature Communications thanks the anonymous reviewers for their contribution to the peer review of this work. Peer review reports are available.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

These authors contributed equally: Silvia Conti, Lorenzo Pimpolari.

Supplementary information

Supplementary information is available for this paper at 10.1038/s41467-020-17297-z.

References

- 1.Huang S, Liu Y, Zhao Y, Ren Z, Guo CF. Flexible electronics: stretchable electrodes and their future. Adv. Funct. Mater. 2019;29:1805924. [Google Scholar]

- 2.Wang C, et al. Advanced carbon for flexible and wearable electronics. Adv. Mater. 2019;31:1801072. doi: 10.1002/adma.201801072. [DOI] [PubMed] [Google Scholar]

- 3.Tobjörk D, Österbacka R. Paper electronics. Adv. Mater. 2011;23:1935–1961. doi: 10.1002/adma.201004692. [DOI] [PubMed] [Google Scholar]

- 4.Ha D, Fang Z, Zhitenev NB. Paper in electronic and optoelectronic devices. Adv. Electron. Mater. 2018;4:1–20. doi: 10.1002/aelm.201700593. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 5.Lessing J, et al. Inkjet printing of conductive inks with high lateral resolution on omniphobic ‘rF paper’ for paper-based electronics and MEMS. Adv. Mater. 2014;26:4677–4682. doi: 10.1002/adma.201401053. [DOI] [PubMed] [Google Scholar]

- 6.Brunetti, F. et al. Printed solar cells and energy storage devices on paper substrates. Adv. Funct. Mater. 29, 1806798 (2019).

- 7.Zhang Y, et al. Flexible electronics based on micro/nanostructured paper. Adv. Mater. 2018;30:1801588. doi: 10.1002/adma.201801588. [DOI] [PubMed] [Google Scholar]

- 8.Zschieschang U, Klauk H. Organic transistors on paper: a brief review. J. Mater. Chem. C. 2019;7:5522–5533. [Google Scholar]

- 9.Akinwande D, Petrone N, Hone J. Two-dimensional flexible nanoelectronics. Nat. Commun. 2014;5:5678. doi: 10.1038/ncomms6678. [DOI] [PubMed] [Google Scholar]

- 10.Franklin AD. Nanomaterials in transistors: from high-performance to thin-film applications. Science. 2015;349:aab2750-1–aab2750-9. doi: 10.1126/science.aab2750. [DOI] [PubMed] [Google Scholar]

- 11.Hernandez Y, et al. High-yield production of graphene by liquid-phase exfoliation of graphite. Nat. Nanotechnol. 2008;3:563–568. doi: 10.1038/nnano.2008.215. [DOI] [PubMed] [Google Scholar]

- 12.Torrisi F, et al. Inkjet-printed graphene electronics. ACS Nano. 2012;6:2992–3006. doi: 10.1021/nn2044609. [DOI] [PubMed] [Google Scholar]

- 13.Finn DJ, et al. Inkjet deposition of liquid-exfoliated graphene and MoS2 nanosheets for printed device applications. J. Mater. Chem. C. 2014;2:925–932. [Google Scholar]

- 14.Withers F, et al. Heterostructures produced from nanosheet-based inks. Nano Lett. 2014;14:3987–3992. doi: 10.1021/nl501355j. [DOI] [PubMed] [Google Scholar]

- 15.Carey T, et al. Fully inkjet-printed two-dimensional material field-effect heterojunctions for wearable and textile electronics. Nat. Commun. 2017;8:1202. doi: 10.1038/s41467-017-01210-2. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 16.McManus D, et al. Water-based and biocompatible 2D crystal inks for all-inkjet-printed heterostructures. Nat. Nanotechnol. 2017;12:343–350. doi: 10.1038/nnano.2016.281. [DOI] [PubMed] [Google Scholar]

- 17.Hu G, et al. Functional inks and printing of two-dimensional materials. Chem. Soc. Rev. 2018;47:3265–3300. doi: 10.1039/c8cs00084k. [DOI] [PubMed] [Google Scholar]

- 18.Manzeli S, Ovchinnikov D, Pasquier D, Yazyev OV, Kis A. 2D transition metal dichalcogenides. Nat. Rev. Mater. 2017;2:17033. [Google Scholar]

- 19.Gong Y, Carozo V, Li H, Terrones M, Jackson TN. High flex cycle testing of CVD monolayer WS2 TFTs on thin flexible polyimide. 2D Mater. 2016;3:0–6. [Google Scholar]

- 20.Kelly AG, et al. All-printed thin-film transistors from networks of liquid-exfoliated nanosheets. Science. 2017;356:69–73. doi: 10.1126/science.aal4062. [DOI] [PubMed] [Google Scholar]

- 21.Kelly AG, Vega-Mayoral V, Boland JB, Coleman JN. Whiskey-phase exfoliation: exfoliation and printing of nanosheets using Irish whiskey. 2D Mater. 2019;6:045036. [Google Scholar]

- 22.Radisavljevic B, Radenovic A, Brivio J, Giacometti V, Kis A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011;6:147–150. doi: 10.1038/nnano.2010.279. [DOI] [PubMed] [Google Scholar]

- 23.Li J, Naiini MM, Vaziri S, Lemme MC, Östling M. Inkjet printing of MoS2. Adv. Funct. Mater. 2014;24:6524–6531. [Google Scholar]

- 24.Tong X, Ashalley E, Lin F, Li H, Wang ZM. Advances in MoS2-based field effect transistors (FETs) Nano-Micro Lett. 2015;7:203–218. doi: 10.1007/s40820-015-0034-8. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 25.Park, S. & Akinwande, D. First demonstration of high performance 2D monolayer transistors on paper substrates. In 2017 IEEE International Electron Devices Meeting (IEDM) 5.2.1–5.2.4 (IEEE, 2017).

- 26.Choi M, et al. Flexible active-matrix organic light-emitting diode display enabled by MoS2 thin-film transistor. Sci. Adv. 2018;4:1–8. doi: 10.1126/sciadv.aas8721. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 27.Lin Z, et al. Solution-processable 2D semiconductors for high-performance large-area electronics. Nature. 2018;562:254–258. doi: 10.1038/s41586-018-0574-4. [DOI] [PubMed] [Google Scholar]

- 28.Sahatiya P, Badhulika S. Wireless, smart, human motion monitoring using solution processed fabrication of graphene-Mos2 transistors on paper. Adv. Electron. Mater. 2018;4:1700388. [Google Scholar]

- 29.Kim T-Y, et al. Electrical properties of synthesized large-area MoS2 field-effect transistors fabricated with inkjet-printed contacts. ACS Nano. 2016;10:2819–2826. doi: 10.1021/acsnano.5b07942. [DOI] [PubMed] [Google Scholar]

- 30.Kim T-Y, et al. Transparent large-area MoS2 phototransistors with inkjet-printed components on flexible platforms. ACS Nano. 2017;11:10273–10280. doi: 10.1021/acsnano.7b04893. [DOI] [PubMed] [Google Scholar]

- 31.Lim YR, et al. Roll-to-roll production of layer-controlled molybdenum disulfide: a platform for 2D semiconductor-based industrial applications. Adv. Mater. 2018;30:1705270. doi: 10.1002/adma.201705270. [DOI] [PubMed] [Google Scholar]

- 32.Xu X, et al. High‐performance monolayer MoS2 films at the wafer scale by two‐step growth. Adv. Funct. Mater. 2019;29:1901070. [Google Scholar]

- 33.Rice C, et al. Raman-scattering measurements and first-principles calculations of strain-induced phonon shifts in monolayer MoS2. Phys. Rev. B. 2013;87:081307. [Google Scholar]

- 34.Worsley R, et al. All-2D material inkjet-printed capacitors: toward fully printed integrated circuits. ACS Nano. 2019;13:54–60. doi: 10.1021/acsnano.8b06464. [DOI] [PubMed] [Google Scholar]

- 35.Lu S, et al. Flexible, print-in-place 1D–2D thin-film transistors using aerosol jet printing. ACS Nano. 2019;13:11263–11272. doi: 10.1021/acsnano.9b04337. [DOI] [PubMed] [Google Scholar]

- 36.Almora O, et al. Capacitive dark currents, hysteresis, and electrode polarization in lead halide perovskite solar cells. J. Phys. Chem. Lett. 2015;6:1645–1652. doi: 10.1021/acs.jpclett.5b00480. [DOI] [PubMed] [Google Scholar]

- 37.Kong D, et al. Capacitance characterization of elastomeric dielectrics for applications in intrinsically stretchable thin film transistors. Adv. Funct. Mater. 2016;26:4680–4686. [Google Scholar]

- 38.Dutta K, Hazra A, Bhattacharyya P. Ti/TiO2 nanotube array/Ti capacitive device for non-polar aromatic hydrocarbon detection. IEEE Trans. Device Mater. Reliab. 2016;16:235–242. [Google Scholar]

- 39.International Technology Roadmap for Semiconductors–ITRS. Available at: http://www.itrs2.net/.

- 40.Zheng J, et al. High-mobility multilayered MoS2 flakes with low contact resistance grown by chemical vapor deposition. Adv. Mater. 2017;29:1604540. doi: 10.1002/adma.201604540. [DOI] [PubMed] [Google Scholar]

- 41.Wachter S, Polyushkin DK, Bethge O, Mueller T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 2017;8:14948. doi: 10.1038/ncomms14948. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 42.Gao Q, et al. Scalable high performance radio frequency electronics based on large domain bilayer MoS2. Nat. Commun. 2018;9:4778. doi: 10.1038/s41467-018-07135-8. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 43.Veeralingam S, Badhulika S. 2D - SnSe2 nanoflakes on paper with 1D - NiO gate insulator based MISFET as multifunctional NIR photo switch and flexible temperature sensor. Mater. Sci. Semicond. Process. 2020;105:104738. [Google Scholar]

- 44.Huang J, et al. Highly transparent and flexible nanopaper transistors. ACS Nano. 2013;7:2106–2113. doi: 10.1021/nn304407r. [DOI] [PubMed] [Google Scholar]

- 45.Minari T, et al. Room-temperature printing of organic thin-film transistors with π-junction gold nanoparticles. Adv. Funct. Mater. 2014;24:4886–4892. [Google Scholar]

- 46.Fujisaki Y, et al. Transparent nanopaper-based flexible organic thin-film transistor array. Adv. Funct. Mater. 2014;24:1657–1663. [Google Scholar]

- 47.Hyun WJ, et al. All-printed, foldable organic thin-film transistors on glassine paper. Adv. Mater. 2015;27:7058–7064. doi: 10.1002/adma.201503478. [DOI] [PubMed] [Google Scholar]

- 48.Dai S, et al. Intrinsically ionic conductive cellulose nanopapers applied as all solid dielectrics for low voltage organic transistors. Nat. Commun. 2018;9:2737. doi: 10.1038/s41467-018-05155-y. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 49.Kraft U, et al. Low-voltage, high-frequency organic transistors and unipolar and complementary ring oscillators on paper. Adv. Electron. Mater. 2019;5:1800453. [Google Scholar]

- 50.Casula G, et al. Printed, low-voltage, all-organic transistors and complementary circuits on paper substrate. Adv. Electron. Mater. 2020;1901027:1–9. [Google Scholar]

- 51.Martins RFP, et al. Recyclable, flexible, low-power oxide electronics. Adv. Funct. Mater. 2013;23:2153–2161. [Google Scholar]

- 52.Thiemann S, et al. Cellulose-based ionogels for paper electronics. Adv. Funct. Mater. 2014;24:625–634. [Google Scholar]

- 53.Kim SJ, et al. Nonvolatile memory thin-film transistors using biodegradable chicken albumen gate insulator and oxide semiconductor channel on eco-friendly paper substrate. ACS Appl. Mater. Interfaces. 2015;7:4869–4874. doi: 10.1021/am508834y. [DOI] [PubMed] [Google Scholar]

- 54.Gaspar D, et al. Planar dual‐gate paper/oxide field effect transistors as universal logic gates. Adv. Electron. Mater. 2018;4:1800423. [Google Scholar]

- 55.Wang X, Gao Y, Liu Z, Luo J, Wan Q. Flexible low-voltage IGZO thin-film transistors with polymer electret gate dielectrics on paper substrates. IEEE Electron Device Lett. 2019;40:224–227. [Google Scholar]

- 56.Liu N, Yun KN, Yu H-Y, Shim JH, Lee CJ. High-performance carbon nanotube thin-film transistors on flexible paper substrates. Appl. Phys. Lett. 2015;106:103106. [Google Scholar]

- 57.Yoon J, et al. Flammable carbon nanotube transistors on a nitrocellulose paper substrate for transient electronics. Nano Res. 2017;10:87–96. [Google Scholar]

- 58.Yoon J, et al. Highly flexible and transparent multilayer MoS2 transistors with graphene electrodes. Small. 2013;9:3295–3300. doi: 10.1002/smll.201300134. [DOI] [PubMed] [Google Scholar]

- 59.Lan Y-W, et al. Scalable fabrication of a complementary logic inverter based on MoS2 fin-shaped field effect transistors. Nanoscale Horiz. 2019;4:683–688. [Google Scholar]

- 60.Razavi, B. Design of Analog CMOS Integrated Circuits. 2nd edn, 704 (McGraw-Hill Education, 2005).

- 61.Wang Z, et al. Current mirror array: a novel circuit topology for combining physical unclonable function and machine learning. IEEE Trans. Circuits Syst. I Regul. Pap. 2018;65:1314–1326. [Google Scholar]

- 62.Coleman JN, et al. Two-dimensional nanosheets produced by liquid exfoliation of layered materials. Science. 2011;331:568–571. doi: 10.1126/science.1194975. [DOI] [PubMed] [Google Scholar]

- 63.Calabrese G, et al. Inkjet-printed graphene Hall mobility measurements and low-frequency noise characterization. Nanoscale. 2020;12:6708–6716. doi: 10.1039/c9nr09289g. [DOI] [PubMed] [Google Scholar]

- 64.Dumcenco D, et al. Large-area epitaxial monolayer MoS2. ACS Nano. 2015;9:4611–4620. doi: 10.1021/acsnano.5b01281. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 65.Gurarslan A, et al. Surface-energy-assisted perfect transfer of centimeter-scale monolayer and few-layer MoS2 films onto arbitrary substrates. ACS Nano. 2014;8:11522–11528. doi: 10.1021/nn5057673. [DOI] [PubMed] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Supplementary Materials

Descriptions of Additional Supplementary Files

Data Availability Statement

The data that support the findings of this work are available from the corresponding authors upon reasonable request.