Nearly ballistic carbon nanotube array transistors are realized with current densities outmatching conventional semiconductors.

Keywords: Carbon nanotube array, current density, quasi-ballistic, high packing density, silicon, gallium arsenide, field-effect transistor, logic

Abstract

Carbon nanotubes (CNTs) are tantalizing candidates for semiconductor electronics because of their exceptional charge transport properties and one-dimensional electrostatics. Ballistic transport approaching the quantum conductance limit of 2G0 = 4e2/h has been achieved in field-effect transistors (FETs) containing one CNT. However, constraints in CNT sorting, processing, alignment, and contacts give rise to nonidealities when CNTs are implemented in densely packed parallel arrays such as those needed for technology, resulting in a conductance per CNT far from 2G0. The consequence has been that, whereas CNTs are ultimately expected to yield FETs that are more conductive than conventional semiconductors, CNTs, instead, have underperformed channel materials, such as Si, by sixfold or more. We report quasi-ballistic CNT array FETs at a density of 47 CNTs μm−1, fabricated through a combination of CNT purification, solution-based assembly, and CNT treatment. The conductance is as high as 0.46 G0 per CNT. In parallel, the conductance of the arrays reaches 1.7 mS μm−1, which is seven times higher than the previous state-of-the-art CNT array FETs made by other methods. The saturated on-state current density is as high as 900 μA μm−1 and is similar to or exceeds that of Si FETs when compared at and equivalent gate oxide thickness and at the same off-state current density. The on-state current density exceeds that of GaAs FETs as well. This breakthrough in CNT array performance is a critical advance toward the exploitation of CNTs in logic, high-speed communications, and other semiconductor electronics technologies.

INTRODUCTION

Semiconducting single-walled carbon nanotubes (CNTs) are desirable materials for the active channels of field-effect transistors (FETs) because of their high current-carrying capacity (1), high carrier velocity (2, 3), and exceptional electrostatics due to their ultrathin body (4). Room-temperature ballistic transport approaching the quantum conductance limit of 2G0 = 4e2/h = 155 μS was first realized in FETs containing single semiconducting CNTs more than a decade ago, demonstrating the exceptional charge transport characteristics of CNTs (5, 6). Realistic approaches for miniaturizing CNT FETs to cutting-edge dimensions that are similar to or smaller than state-of-the-art Si FETs have been established for single CNT FETs with sub–10-nm channel lengths and covalently bonded end contacts that enable aggressively scaled-down electrodes (1, 7).

Future electronic devices made from CNTs will require multiple CNTs per FET. Modeling based on extrapolation of individual CNT characteristics to parallel, aligned arrays of densely packed but well-spaced semiconducting CNTs (~100 CNTs μm−1) has shown that CNT arrays will outperform conventional semiconductors such as single-crystalline Si in logic devices and radio frequency (RF) amplifiers (8, 9). CNT array FETs are specifically expected to lead to at least a two- to fivefold gain in the energy-delay product of logic devices (8, 10) (thereby enabling faster switching and lower power consumption) while allowing for particularly high-speed RF amplifier devices with excellent linearity (9) (thereby enabling increased data throughput and lower power consumption). These advances in single CNT FETs and the projected characteristics of array FETs have made it clear that CNTs are prime candidates for next-generation semiconductor electronics that promise substantial performance gains.

Recent progress in the alignment of CNTs from solution (11) and via chemical vapor deposition (CVD) (12, 13) processes demonstrates promising scalability; however, achieving the optimal packing density of CNTs in an array and a high conductance per CNT remains to be a challenge. The ideal morphology of CNTs in an array FET consists of a relatively sparse layer of aligned CNTs with a pitch of more than 5 nm (10). It is difficult to form highly conductive contacts to more tightly packed arrays (14), and deleterious inter-CNT interactions arise in tightly packed arrays, which cause screening effects that can decrease both conductance and on/off ratio (Ion/Ioff) (15). In addition, the ideal CNT array consists of purely semiconducting-type CNTs with a homogeneous band gap. Even a single metallic CNT impurity can short-circuit the FET and lower the Ion/Ioff by several orders of magnitude (16).

As a result of these materials science challenges, it has not been possible to approach the quantum conductance limit in FETs based on dense arrays of CNTs while maintaining a high Ion/Ioff. For example, arrays of semiconducting CNTs, sorted using anionic surfactants, have been aligned and deposited onto substrates from solution via Langmuir-Schaefer assembly at a high density of 1100 CNTs μm−1 and have demonstrated a conductance of 0.25 mS μm−1, corresponding to 0.003 G0 or 0.23 μS per CNT (17). Wu et al. have organized surfactant-dispersed CNTs into aligned rafts with a density of 30 CNTs μm−1, demonstrating a conductance of 0.08 mS μm−1, corresponding to 0.04 G0 or 3.2 μS per CNT (18). Aligned arrays of CNTs at a density of 100 CNTs μm−1 grown by CVD and purified via selective Joule heating to remove metallic CNTs have demonstrated a conductance of 0.12 mS μm−1, which corresponds to 0.015 G0 or 1.2 μS per CNT (19). Recent work has also advanced the performance of surfactant-encapsulated and conjugated polymer–wrapped CNTs in aligned arrays prepared by dielectrophoresis (20) and shear-casting (21); however, the conductance has not exceeded 0.01 mS μm−1 in these cases (although the Lch of these types of devices has yet to be aggressively scaled). Advances in the performance of random-network thin-film FETs with Lch on the order of micrometers have been realized (22–25); however, inter-CNT interactions and contact-resistance challenges have limited both the on-state conductance and the Ion/Ioff of random-network FETs when Lch is reduced to hundreds of nanometers (26, 27). In each scenario, the result has been that, whereas CNTs are ultimately expected to yield FETs that are more conductive than conventional semiconductors for logic applications, CNTs, instead, have underperformed channel materials, such as Si, by sixfold or more. Likewise, in RF applications, depressed on-state conductance and imperfect saturation characteristics arising from metallic CNTs and inter-CNT interactions have limited the maximum frequency of oscillation and linearity (9, 27–29).

Here, we report on quasi-ballistic CNT array FETs at a density of 50 CNTs μm−1 prepared through the deposition of highly purified polyfluorene-sorted semiconducting CNTs from solution into aligned arrays on substrates via the scalable process of floating evaporative self-assembly (FESA) (30–32). The arrays achieve exceptional performance because of three reasons. The (i) outstanding alignment and spacing of the CNTs in the arrays afforded by FESA and the (ii) postdeposition treatment of the arrays to remove solvent residues and the insulating side chains of the polyfluorene wrappers enable the realization of highly conductive electrical contacts to each CNT in the arrays and a highly conductive channel. As a result, the device conductance reaches 1.7 mS μm−1 at an Lch of 100 nm and as high as 0.46 G0 or 35 μS per CNT. At the same time, the (iii) exceptional electronic-type purity of the semiconducting CNTs afforded by the use of polyfluorenes as CNT-differentiating agents leads to a high Ion/Ioff. The saturated on-state current density reaches 900 μA μm−1 and exceeds that of Si FETs when compared at an equivalent gate oxide thickness and at the same off-state current density.

RESULTS

FET architecture

The FETs are fabricated by isolating semiconducting CNTs first using a large excess of the conjugated polymer poly[(9,9-dioctylfluorenyl-2,7-diyl)-alt-co-(6,60-(2,20-bipyridine))] (PFO-BPy) in toluene to selectively wrap the semiconducting species (33). Recent work has shown that polyfluorenes (34), polythiophenes (35), and related copolymers (36) can selectivity isolate semiconducting CNTs to high purities, and advances in the detection of metallic CNTs via electronic (21, 31) and spectroscopic (37) measurement indicate that the electronic-type purity of these polymer-sorted CNTs is >99.98% semiconducting. The CNTs are deposited onto Si wafers with 15 nm of thermally grown SiO2 via FESA, which yields dense arrays of CNTs that remain predominantly isolated. FETs are fabricated from the CNTs after three different stages of postdeposition treatment: (i) immediately after FESA deposition (“as-deposited”), (ii) after extensive solvent rinsing (“rinsed”), and (iii) after extensive solvent rinsing followed by an additional thermal annealing step in high vacuum (“rinsed + annealed”). Previous work has shown that postdeposition rinsing (38–40) and annealing, for example, in vacuum (17, 18) or oxidizing environments (41), can be used to desorb and/or decompose spurious adsorbates and surfactants from the surfaces of CNTs. Here, these postdeposition treatments are implemented to specifically remove residues arising from solution processing in chloroform and to partially decompose the polymer wrappers, with the goals of improving the CNT conductance and electrical contacts, as detailed below.

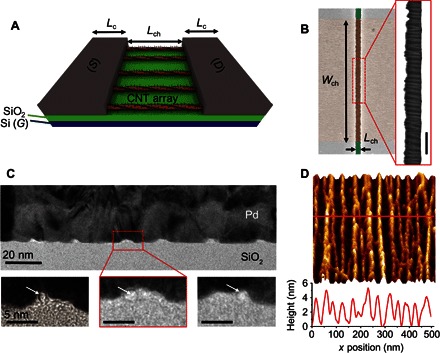

The schematic in Fig. 1A and the scanning electron microscopy (SEM) image in Fig. 1B depict the device architecture. The SiO2 and Si substrate are used as the FET back-gate dielectric and gate electrode, respectively. The source and drain electrodes consist of thermally deposited and patterned 30-nm-thick layers of Pd. The length over which each metal contact overlaps the CNT array (Lc) is 6.8 ± 0.4 μm, the channel width (Wch) is 4 μm, and Lch varies from 95 to 340 nm. The high-resolution SEM image of a representative channel in Fig. 1B demonstrates that the semiconducting CNTs are well aligned and predominantly isolated at a density of 47 ± 3 CNTs μm−1. The electrode regions are characterized via cross-sectional transmission electron (Fig. 1C) and atomic force micrographs (Fig. 1D), which show that the Pd conforms to the CNT arrays and the underlying SiO2 substrate.

Fig. 1. FETs constructed from densely packed semiconducting CNT arrays.

(A) Schematic of CNT array sitting on a SiO2/Si back gate (G) with top Pd source (S) and drain (D) electrodes. (B) False-colored SEM image of a representative FET highlighting where the contacts overlap the CNT array (light orange) and the CNT array channel (dark orange), with Wch = 4.1 μm and Lch = 150 nm. Inset SEM image (scale bar, 200 nm) shows the CNT array, with 47 CNTs μm−1 and a high degree of alignment. (C) TEM cross-sectional image of Pd/CNT/SiO2 electrode stack where the “humps” in the Pd correspond to CNTs in the array. High-resolution TEM images reveal individual CNTs underneath the Pd “humps” with a diameter of 1.3 to 1.9 nm. (D) Atomic force miscroscopy image of 30 nm of Pd overcoating a CNT array, evidencing the conformity of the Pd to the individual CNTs.

Current-voltage characteristics

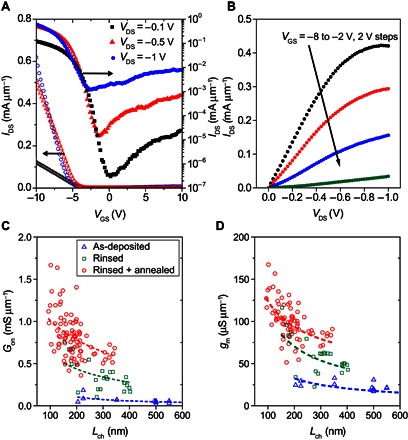

The IDS-VGS and IDS-VDS characteristics presented in Fig. 2 (A and B, respectively) demonstrate the behavior of a typical “rinsed + annealed” array FET at an Lch of 100 nm (full sweep IDS-VGS characteristics presented in fig. S1). IDS increases nearly linearly with VGS for VGS less than a threshold voltage (VT) of roughly −4 V (Fig. 2A) and ohmically with VDS from 0 to −0.3 V. IDS then increases sublinearly for VDS > −0.3 V, with current saturation at VDS = −1 V (Fig. 2B). Saturation has been reported previously in single CNT FETs at similar biases and Lch and has been attributed to optical phonon scattering that occurs at high fields (5).

Fig. 2. Electrical properties of CNT array FETs and influence of postdeposition treatment on conductance.

(A) IDS-VGS curves forward sweep for a representative “rinsed + annealed” FET with Lch = 100 nm where the open and filled symbols are plotted on linear and logarithmic scales, respectively. (B) IDS-VDS output curves for the same device as in (A). (C) Gon versus Lch obtained from CNT arrays that have undergone the three different postdeposition treatment conditions, fit to Eq. 1, with a sevenfold total increase in Gon resulting from the “rinsed + annealed” treatment. (D) gm versus Lch for each surface treatment fit to as a guide to the eye, with a threefold total increase in gm resulting from the “rinsed + annealed” treatment.

To compare the effect of the different postdeposition CNT treatments, the on-state conductance (Gon) is extracted from the transfer characteristics at VDS = −0.1 V and VGS = −10 V, and the transconductance (gm = dIDS/dVGS) is extracted by performing a linear fit to IDS-VGS curves measured at VDS = −1 V in the linear region where VGS < VT. Gon, in some cases, is so high that the lead resistance (Rleads) is nonnegligible, approaching 23% of the on-state device resistance, and is measured and then subtracted to determine the intrinsic FET characteristics (as detailed in fig. S2). Both Gon and gm generally increase with decreasing Lch for all three postdeposition treatments. When analyzed at similar Lch, the postdeposition treatments increase Gon sevenfold (Fig. 2C) and gm threefold (Fig. 2D) in total. Gon reaches as high as 1.7 mS μm−1 following the “rinsed + annealed” treatment at Lch = 100 nm while maintaining an Ion/Ioff of 105 at VDS = −0.1 V. A gm of 170 μS μm−1 and a saturation current (Isat) of 900 μA μm−1 are achieved in the same device at VDS = −1 V, although at a lower Ion/Ioff of 102.7. When all 88 “rinsed + annealed” FETs plotted in Fig. 2 (C and D) with an Lch of 190 ± 60 nm are considered, we obtain a Gon of 0.8 ± 0.3 mS μm−1 at an Ion/Ioff of 105.5±1.3 for a VDS of −0.1 V. Likewise, we obtain a gm of 99 ± 25 μS μm−1 and an Isat of 490 ± 140 μA μm−1 at an Ion/Ioff of 103.9±1.0 for a VDS of −1 V. The lower Ion/Ioff at higher VDS is attributed to increased electron injection and ambipolar behavior, possibly originating from inter-CNT crosstalk effects that may affect injection at the CNT-drain interface for VGS > VT (15, 42). Nonetheless, for 60% of “rinsed + annealed” CNT array FETs measured at VDS = −1 V, the Ioff is still lower than 0.1 μA μm−1, approaching the off-state needed for high-performance logic applications (8, 43). The Ion/Ioff at low VDS is more indicative of the metal-semiconducting CNT purity. For the “rinsed + annealed” devices, the Ion/Ioff at low VDS exceeds 103 in 87 of 88 devices measured, indicating that the purity of the semiconducting CNTs is at least 99.99%. The majority of the devices (70%) exhibit excellent Ion/Ioff greater than 105.

Critically, these high Ion/Ioff ratios are obtained without the need for metallic CNT burnout techniques, such as Joule self-heating (12, 44), which can degrade the conductance of remaining semiconducting CNTs and become increasingly difficult to implement with increasing CNT packing density. It is also important to note that the high Ion/Ioff ratios obtained here are not the result of the preferential etching or removal of metallic CNTs during the rinsing or annealing treatments. For example, the off-state conductance is similar in devices fabricated without and with 400°C annealing treatment, reaching 10−8.2±1.8 and 10−8.7±1.2 S μm−1, respectively. Additional discussion of the semiconducting purity and of the factors that may affect the Ion/Ioff is further elaborated in the Supplementary Materials and in figs. S3 to S5.

The Gon versus Lch dependencies for each of the postdeposition treatments in Fig. 2C are fit to extract the mean free path (LMFP) according to

| (1) |

where h/4e2 is the quantum resistance for two modes (45) and 2Rc is the total CNT-Pd contact resistance at both source and drain electrodes. The fit LMFP are 3, 21, and 42 nm for the “as-deposited,” “rinsed,” and “rinsed + annealed” CNTs, respectively. From these results, we postulate that charge transport in the “as-deposited” CNT arrays is significantly limited by impurity scattering and that postdeposition treatments reduce impurities (that is, increase LMFP). Moreover, whereas the CNT-Pd contacts are nonohmic in the “as-deposited” FETs, possibly indicating the presence of a Schottky barrier (46, 47), the contacts become ohmic in “rinsed + annealed” devices (fig. S6).

Characterization of postdeposition treatments

In general, optimizing the performance of FETs fabricated from solution-deposited CNTs is challenging because (i) solution-processed CNTs are coated with relatively insulating surfactant/polymer wrappers that can interfere with contacts (48) and (ii) the exposure of the CNTs to solvent and the ultrasonic processing used to disperse the CNTs can physically and chemically modify their surfaces and properties, potentially decreasing LMFP and conductance (49, 50). X-ray photoelectron spectroscopy (XPS), optical absorption, and Fourier transform infrared (FTIR) spectroscopy are used to characterize the modification of our CNTs in their “as-deposited” state and to show that this modification is largely reversible through postdeposition treatment.

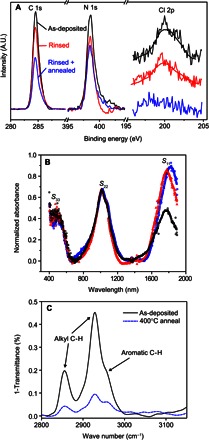

In the “as-deposited” CNT arrays, the atomic ratio of C/N measured by XPS is 39:1 (Fig. 3A), which is similar to the ratio of 41:1 measured from the optical absorbance spectra of the polymer-wrapped CNTs in solution (fig. S7) using known optical cross sections to determine relative concentrations. These data indicate that the PFO-BPy polymer wrapper and the CNTs are nearly equally abundant in the “as-deposited” arrays by mass, corresponding to up to six polymer chains wrapping around a given CNT cross section. Cl residues are also detected at a concentration of (1.7 ± 0.5) × 1013 cm−2 or a C/Cl ratio of 160:1. Moreover, the CNT excitonic S11 absorption peak is heavily bleached, indicating the chemical modification and/or doping of the CNTs (51). Previous work has shown that processing in chlorinated solvents can partially chlorinate CNTs (49, 52), potentially explaining the excess Cl residues, the doping, and, therefore, the poor LMFP. The protocols used to quantify atomic concentrations from XPS and optical absorbance spectra and a summary of these concentrations are given in figs. S7 and S8 and table S1.

Fig. 3. Spectroscopic characterization of postdeposition treatments.

(A) XPS of CNT arrays showing C 1s, N 1s, and Cl 2p peaks following solvent rinsing and vacuum annealing. A.U., arbitrary units. (B) Optical absorbance spectra of CNT array films deposited on quartz with the approximate spectral windows corresponding to the first three CNT Sii transitions marked for clarity. Black open circles correspond to “as-deposited,” red open triangles correspond to “rinsed,” and blue open squares correspond to “rinsed + annealed” treatments. (C) FTIR spectroscopy of 10-nm-thick PFO-BPy films. Vacuum annealing reduces the alkyl C–H stretching modes centered at 2855 and 2926 cm−1, corresponding to loss of the polymer side chains.

Postdeposition rinsing and vacuum annealing treatments are investigated as means for minimizing/decomposing the insulating polymer wrapper and for removing the Cl residues. The S11 peak is largely restored, and 54 ± 5% of the Cl is removed in “rinsed” arrays. However, only minor amounts of C and N of 8.5 ± 2.5% and 8.9 ± 3.2%, respectively, are removed, indicating that most of the CNTs and the polymer wrapper remain on the substrate surface during this rinsing. Annealing in vacuum is next explored. High-vacuum (as opposed to oxidizing) conditions are used to preserve the pristine nature of the CNTs. The FTIR spectra in Fig. 3C and fig. S9 indicate loss of the polymer’s alkyl side chains (53) between 300° and 400°C (as assessed from C–H stretch modes at 2855 and 2926 cm−1) in “rinsed + annealed” arrays. Annealing at 400°C also eliminates all signatures of Cl and maximizes the S11. Thus, vacuum annealing at 400°C is chosen as the annealing condition here. XPS and FTIR show that the backbone of the PFO-BPy wrapper is still partly intact under this condition (Fig. 3A and fig. S9). Nonetheless, the “rinsed + annealed” treatment has a combined effect of removing adsorbed Cl, reversing the chemical modification of the CNTs, and removing the insulating side chains of the polymer. These effects increase the LMFP from 3 to 42 nm while also leading to ohmic CNT-Pd contacts, giving rise to the seven- and threefold improvements in Gon and gm, respectively.

Further increasing the annealing temperature to 500°C does not yield additional improvements in Gon. For example, Gon is statistically invariant, changing from 0.8 ± 0.3 to 0.7 ± 0.3 when the annealing temperature is increased from 400° to 500°C, respectively, for devices with Lch in the range of 100 to 300 nm. Gon is invariant despite the observation that the carbon-carbon double bond stretch arising from the polymer backbone at 1450 cm−1 begins to decay between 400° and 500°C (fig. S9). The lack of improvement in Gon using a 500°C anneal suggests that the removal of the spurious Cl and polymer side chains between 300° and 400°C is the main factor responsible for the conductance increase observed during annealing. Additional studies show that annealing at 400°C without rinsing first also effectively removes the Cl and side chains and that “annealed-only” devices demonstrate a similar Gon to “rinsed + annealed” FETs (fig. S10). Regardless, the rinsing treatment provides a valuable route to improve device performance for applications that require low-temperature processing (for example, plastic electronics).

DISCUSSION

FET benchmarking compared to CNT FETs

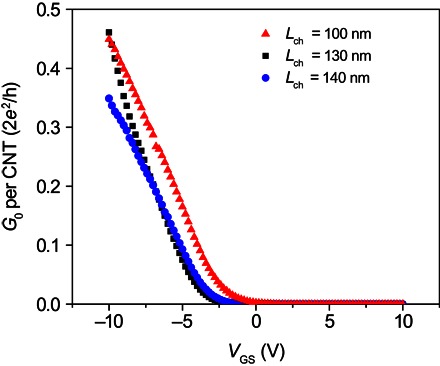

The performance of the CNT arrays measured in this work are compared (i) to state-of-the-art single CNT FETs on a per-tube basis in Fig. 4 and (ii) to commercially fabricated Si metal oxide semiconductor FETs (MOSFETs) in Fig. 5. The highest reported conductance in a CVD-grown single CNT FET is 1.4 G0 with a 2Rc of 10 kilohm-tube and an LMFP of 200 nm at an Lch of 15 nm (54). For comparison, the highest reported conductance in a solution-processed single CNT FET is 0.58 G0 with a 2Rc of 20 kilohm-tube and an LMFP of 28 nm at an Lch of 15 nm (55). The conductance per tube of three champion CNT array FETs from this study are presented in Fig. 4 as a function of VGS at a VDS = −0.1 V. The conductance per tube reaches 0.46 G0 at a much longer Lch of 130 nm. The average conductance per tube is 0.31 ± 0.08 G0 for Lch < 150 nm (measurement and comparison to previous state-of-the-art CNT arrays are further detailed in fig. S11 and table S2). Analysis of more than 88 devices at different Lch via the transmission line and Y-function methods in fig. S12 indicates that the characteristic 2Rc of these devices falls within the range of 28 to 40 kilohm-tube, whereas the LMFP varies from 33 to 56 nm, corresponding to drift-diffusion mobility in the range of 1130 to 1912 cm2 V−1 s−1. Scaling of the Lch below the LMFP (<30 nm) should lead to further increases in the channel conductance, thereby approaching the performance of state-of-the-art CVD-grown single CNT FETs, but in a many-CNT array that is more useful for commercial technologies.

Fig. 4. CNT array FETs with conductance per tube approaching the fundamental quantum conductance limit 2G0 = 4e2/h.

Three champion devices with conductance reaching 0.46 G0. All three devices also exhibit high Ion/Ioff > 104.

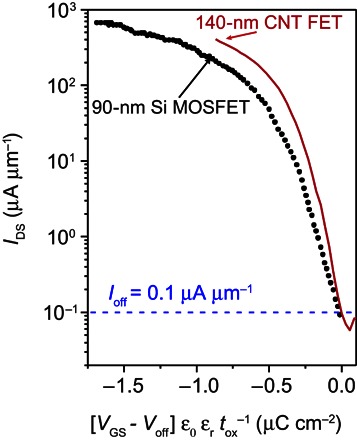

Fig. 5. Benchmarking CNT array FET performance against Si MOSFETs.

Isat of a champion CNT array FET (VDS = −1 V; Lch = 140 nm) and 90-nm node Si MOSFET (43) (VDS = −1.2 V) versus VGS − Voff, normalized by the dielectric constant of the gate dielectric (εrεo) and the gate oxide thickness (tox), where VGS − Voff is 0 V at an Ioff of 0.1 μA μm−1. Oxide parameters for the CNT array FET are tox = 15 nm and εr = (εair + εSiO2)/2 = 2.45 for the SiO2/CNT/air dielectric stack (31, 62). Oxide parameters for the Si MOSFET are tox = teff = 2.4 nm [effective oxide thickness accounting for inversion capacitance (63)] and εr = εSiO2 = 3.9. The champion CNT array FET exhibits an Isat that is 1.9-fold higher when measured at an equivalent charge density (VGS − Voff) εrεotox−1 of −0.85 μC cm−2.

FET benchmarking compared to Si FETs

Comparison of CNT FETs to Si MOSFETs has become a useful benchmarking tool for evaluating the fundamental limits of scaling the channel length (1), contact length (7, 48), and CNT density of CNT FETs (19). For digital logic applications, a high drive current and a high transconductance are required to maximize speed (that is, logic transitions per second), whereas the subthreshold slope must be high to minimize leakage current when the device is switched off (56). We benchmark the saturated on-state current and the subthreshold behaviors of CNT array FETs against a 90-nm node Si P-channel MOSFET (43) at an equivalent oxide thickness and an off-state current density of 0.1 μA μm−1 in Fig. 5. The CNT array FET exhibits a more rapid rise in IDS than the Si MOSFET, indicative of the excellent electrostatic properties of the thin-body CNTs. The CNT array FET also shows significant improvements in the on-state where, at an equivalent charge density (VGS − Voff) εrεotox−1 of −0.85 μC cm−2, CNT array FETs reach an Isat of 392 μA μm−1, which is 1.9 times higher than the MOSFET Isat of 204 μA μm−1. We also note that the champion 100-nm Lch CNT array FET with a current density of 900 μA μm−1 exceeds the 630 μA μm−1 that has been demonstrated for the GaAs pseudomorphic high-electron mobility transistor (pHEMT) technology (57, 58).

CONCLUSIONS

Ballistic transport with an on-state conductance approaching 2G0 has been previously realized in single CNT FETs but has been difficult to achieve in FETs constructed from densely packed arrays of CNTs, such as those needed for most technologies. CNT array FETs are demonstrated here with an on-state conductance of 1.7 mS μm−1 and a conductance per CNT as high as 0.46 G0, which is seven times higher than previous state-of-the-art CNT array FETs made by other methods. These FETs are nearing the performance of state-of-the-art single CNT FETs but in the format of an array in which quasi-ballistic transport is simultaneously driven through many, tightly packed CNTs in parallel, substantially improving the absolute current drive of the FETs and, therefore, their utility in technologies.

The exceptional performance of the arrays achieved here is attributed to the combined outstanding alignment and spacing of the CNTs, the postdeposition treatment of the arrays to remove solvent residues and the insulating side chains of the polymers that wrap the CNTs, and the exceptional electronic-type purity of the semiconducting CNTs afforded by the use of polyfluorenes as CNT-differentiating agents. The performance of previous CNT array FETs has not been as high, likely because these FETs have not simultaneously met all of these attributes. For example, the alignment and postdeposition treatment of CNTs alone are insufficient but must be coupled with the proper CNT array packing density and morphology to avoid inter-CNT interactions that can lower Gon and on-off switching, high semiconducting purity to avoid leakage currents from metallic CNTs, and the use of CNTs that have not undergone significant chemical modification to achieve a long LMFP and high channel conductance. As a result of the excellent alignment and spacing, postdeposition treatment, and high electronic-type purity achieved here, on-state and subthreshold behaviors that are comparable to or that exceed those of state-of-the-art Si MOSFETs are realized, when compared at an equivalent gate oxide thickness and at the same off-state current density.

A number of challenges remain, including reducing hysteresis (22), improving device-to-device reproducibility (59), reducing leakage current (60), and scaling contact length for both N- and P-channel FETs (7). However, recent successes in overcoming these challenges in single CNT (7, 60, 61) and random-network CNT (22, 59) devices should translate well to the array CNT FETs presented here, providing an increasingly realistic pathway toward the development of CNT electronics and the application of these exceptional one-dimensional semiconductors in next-generation logic, high-speed communications, and semiconductor electronics technologies.

MATERIALS AND METHODS

Preparation of PFO-BPy–wrapped semiconducting CNT solutions

Semiconducting CNTs were extracted from arc-discharge CNT soot (750514, Sigma-Aldrich). A 1:1 weight ratio of PFO-BPy (2 mg ml−1; ADS153UV, American Dye Source) and CNTs was mixed in 60 ml of toluene. Raw CNT solution was ultrasonicated using a Fisher sonic dismembrator model 500 (400 W) at 40% amplitude for 5 min. Next, the solution was divided into six tubes that were centrifuged with a swing bucket rotor (Sorvall WX, TH-641, Thermo Scientific) at 300,000g for 10 min to remove soot and undispersed CNTs. The upper 90% of the supernatant was collected and centrifuged again at 300,000g for 1 hour. This process was repeated for up to six batches, and then the supernatants were collected, combined, and distilled down to a volume of 60 ml. The concentrated solution was next centrifuged to form a pellet that was then collected and redispersed in toluene, and the PFO-BPy–rich supernatant was discarded. This pelleting and redispersion process was repeated until a 1:1 mass ratio of PFO-BPy to CNT was achieved. After the initial sorting and polymer washing steps, the PFO-BPy–wrapped CNT pellets were dispersed in chloroform (stabilized with ethanol, used as is from Fisher Scientific, #C606SK-1) at a concentration of 10 μg ml−1. The concentration of the CNTs was determined using known optical cross sections at the S22 transition (33), as explained in the Supplementary Materials. The concentration of PFO-BPy was optically determined from a series of reference samples of known concentration.

Deposition of CNT arrays

The CNT ink suspended in chloroform was delivered to substrates via FESA (30) in discrete ~0.6- to 1.2-μl doses onto the surface of a water subphase every 0.2 to 0.4 s using a syringe pump. Simultaneously, a receiving substrate that was partially submerged in the aqueous subphase was pulled out at a constant lift rate of 5 mm min−1. The ink droplets spread on the water, wet the surface of the receiving substrate, and then evaporated. Each dose of ink resulted in the deposition of a band of aligned CNTs that was approximately 100 μm tall and spanned the entire width of the substrate, which was typically ~25 mm wide.

Fabrication of CNT FETs

The CNT channels of neighboring FETs were isolated from one another by patterning the deposited films of aligned CNTs before postdeposition treatments. The channels were protected by 4 μm × 10 μm regions of polymethylmethacrylate (PMMA) that were patterned using electron-beam lithography. An oxygen reactive ion etch was used to etch the unwanted regions of CNTs, and then the remaining PMMA was lifted off with acetone. After the postdeposition treatments, a second electron-beam lithography step was performed to define source-drain electrodes with various channel lengths. Contacts were formed via thermal deposition of Pd (30 nm) and lift-off in acetone. The devices were measured under ambient conditions directly after electrode patterning with no further treatments. There is hysteresis in the I-V characteristics (fig. S1), which is expected for unencapsulated CNT FETs exposed to ambient conditions. Negative to positive sweeps (VG) are shown in Figs. 2, 4, and 5.

Postdeposition treatment of the CNT arrays

The “rinsed” samples were treated by submerging the patterned CNT arrays in a vial of toluene at 60°C for 1 hour. Upon completion, the sample was transferred immediately into a room-temperature isopropyl bath for 30 s, followed by drying in an air stream. The “rinsed + annealed” samples underwent the “rinsed” treatment followed by annealing in vacuum at a base pressure of 5 × 10−6 torr and temperature of 400°C for 1 hour.

X-ray photoelectron spectroscopy

CNT arrays were prepared via FESA, as described above. Each substrate was broken into four equivalent parts, which underwent “as-deposited,” “rinsed,” “annealed,” and “rinsed + annealed” treatments. The XPS spectra were measured using a Thermo K-Alpha XPS with an x-ray spot size of 400 μm and monochromatic Al Kα radiation (1486.7 eV). Survey and individual spectra were acquired using analyzer pass energies of 188 and 50 eV, respectively.

Fourier transform infrared spectroscopy

PFO-BPy thin films were prepared for FTIR analysis by spin-casting a solution of PFO-BPy (3 mg ml−1) in chlorobenzene at a rate of 2000 rpm onto double-side polished Si/SiO2 substrates. FTIR spectra were measured in transmission mode using a Bruker Vertex 70 with a Hyperion 2000 microscope having an approximately 250 μm × 250 μm spot size.

Cross-sectional TEM imaging

CNT arrays were prepared via FESA on SiO2 (90 nm)/Si substrates. The cross section was prepared using the in situ focused ion beam (FIB) lift-out technique on an FEI Dual Beam FIB/SEM. The sample was capped with Ir and ePt/IPt before prep and imaged with a FEI Tecnai TF-20 field emission gun/TEM operated at 200 kV in bright-field and high-resolution TEM mode (Evans Analytical Group).

Supplementary Material

Acknowledgments

We acknowledge insightful discussion with C. Rutherglen and the team at Carbonics Inc. We also recognize M. Kats (Department of Electrical and Computer Engineering, University of Wisconsin-Madison) for providing access to FTIR instrumentation. Funding: We acknowledge support from NSF grants CMMI-1129802 and CMMI-1462771 for research on scaled CNT alignment, deposition, and device fabrication (G.J.B., H.T.E, P.G., and M.S.A.); Carbonics Inc. (prime contractor) under the Air Force contract FA8750-15-C-0257 for work on contact-resistance optimization (G.J.B. and M.S.A.); the U.S. Army Research Office contract W911NF-12-1-0025 for materials characterization of the postdeposition treatments (A.J.W., N.S.S., and M.S.A.); and NSF grant DMR-1350537 for electronic-type purity studies (G.J.B. and M.S.A.). We also acknowledge support from NSF graduate research fellowship grant DGE-1256259 (G.J.B. and A.J.W.). Author contributions: G.J.B. and M.S.A. conceived the postdeposition treatments and device studies; G.J.B. fabricated and tested the FET devices; G.J.B., H.T.E., P.G., and M.S.A. designed, built, and implemented a custom apparatus for scaled CNT deposition and alignment via FESA; G.J.B., A.J.W., and N.S.S. performed the spectroscopic characterization of the postdeposition treatments; and all authors analyzed the data and contributed to the writing of the manuscript. Competing interests: The authors declare that they have no competing interests. Data and materials availability: All data needed to evaluate the conclusions in the paper are present in the paper and/or the Supplementary Materials. Additional data related to this paper may be requested from the authors.

SUPPLEMENTARY MATERIALS

Supplementary material for this article is available at http://advances.sciencemag.org/cgi/content/full/2/9/e1601240/DC1

Supplementary Text

fig. S1. Full sweep transfer characteristics.

fig. S2. Lead resistance subtraction.

fig. S3. Optical spectroscopy evidence of high semiconducting purity.

fig. S4. Effect of annealing on Ion/Ioff.

fig. S5. Ioff variability.

fig. S6. Postdeposition treatment effect on output characteristics.

fig. S7. Optical absorbance spectra used to verify XPS atomic concentrations and CNT diameter distribution.

fig. S8. Atomic force microscopy height measurement used to quantify packing density for XPS calibration.

fig. S9. Temperature-dependent FTIR measurement of PFO-BPy side chains and backbone.

fig. S10. On-conductance comparison of “annealed” versus “rinsed + annealed” treatments.

fig. S11. Conductance per tube measured for FETs with Lch < 150 nm.

fig. S12. Contact resistance and mean free path extraction.

table S1. Surface treatment XPS summary.

table S2. CNT FET performance comparisons.

REFERENCES AND NOTES

- 1.Franklin A. D., Luisier M., Han S.-J., Tulevski G., Breslin C. M., Gignac L., Lundstrom M. S., Haensch W., Sub-10 nm carbon nanotube transistor. Nano Lett. 12, 758–762 (2012). [DOI] [PubMed] [Google Scholar]

- 2.Lee C.-S., Pop E., Franklin A. D., Haensch W., Wong H.-S. P., A compact virtual-source model for carbon nanotube FETs in the sub-10-nm regime—Part I: Intrinsic elements. IEEE T. Electron. Dev. 62, 3061–3069 (2015). [Google Scholar]

- 3.Lundstrom M. S., Antoniadis D. A., Compact models and the physics of nanoscale FETs. IEEE T. Electron. Dev. 61, 225–233 (2014). [Google Scholar]

- 4.Avouris P., Chen Z., Perebeinos V., Carbon-based electronics. Nat. Nanotechnol. 2, 605–615 (2007). [DOI] [PubMed] [Google Scholar]

- 5.Javey A., Guo J., Wang Q., Lundstrom M., Dai H., Ballistic carbon nanotube field-effect transistors. Nature 424, 654–657 (2003). [DOI] [PubMed] [Google Scholar]

- 6.Chen Z., Appenzeller J., Knoch J., Lin Y.-m., Avouris P., The role of metal–nanotube contact in the performance of carbon nanotube field-effect transistors. Nano Lett. 5, 1497–1502 (2005). [DOI] [PubMed] [Google Scholar]

- 7.Cao Q., Han S.-J., Tersoff J., Franklin A. D., Zhu Y., Zhang Z., Tulevski G. S., Tang J., Haensch W., End-bonded contacts for carbon nanotube transistors with low, size-independent resistance. Science 350, 68–72 (2015). [DOI] [PubMed] [Google Scholar]

- 8.Tulevski G. S., Franklin A. D., Frank D., Lobez J. M., Cao Q., Park H., Afzali A., Han S.-J., Hannon J. B., Haensch W., Toward high-performance digital logic technology with carbon nanotubes. ACS Nano 8, 8730–8745 (2014). [DOI] [PubMed] [Google Scholar]

- 9.Rutherglen C., Jain D., Burke P., Nanotube electronics for radiofrequency applications. Nat. Nanotechnol. 4, 811–819 (2009). [DOI] [PubMed] [Google Scholar]

- 10.Zang J., Lin A., Patil N., Wei H., Wei L., Wong H.-S. P., Mitra S., Carbon nanotube robust digital VLSI. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 31, 453–471 (2012). [Google Scholar]

- 11.He X., Gao W., Xie L., Li B., Zhang Q., Lei S., Robinson J. M., Hároz E. H., Doorn S. K., Wang W., Vajtai R., Ajayan P. M., Adams W. W., Hauge R. H., Kono J., Wafer-scale monodomain films of spontaneously aligned single-walled carbon nanotubes. Nat. Nanotechnol. 11, 633–638 (2016). [DOI] [PubMed] [Google Scholar]

- 12.Jin S. H., Dunham S. N., Song J., Xie X., Kim J.-h., Lu C., Islam A., Du F., Kim J., Felts J., Li Y., Xiong F., Wahab M. A., Menon M., Cho E., Grosse K. L., Lee D. J., Chung H. U., Pop E., Alam M. A., King W. P., Huang Y., Rogers J. A., Using nanoscale thermocapillary flows to create arrays of purely semiconducting single-walled carbon nanotubes. Nat. Nanotechnol. 8, 347–355 (2013). [DOI] [PubMed] [Google Scholar]

- 13.Ryu K., Badmaev A., Wang C., Lin A., Patil N., Gomez L., Kumar A., Mitra S., Wong H.-S. P., Zhou C., CMOS-analogous wafer-scale nanotube-on-insulator approach for submicrometer devices and integrated circuits using aligned nanotubes. Nano Lett. 9, 189–197 (2009). [DOI] [PubMed] [Google Scholar]

- 14.Perebeinos V., Tersoff J., Wetting transition for carbon nanotube arrays under metal contacts. Phys. Rev. Lett. 114, 085501 (2015). [DOI] [PubMed] [Google Scholar]

- 15.Léonard F., Crosstalk between nanotube devices: Contact and channel effects. Nanotechnology 17, 2381–2385 (2006). [Google Scholar]

- 16.Tulevski G. S., Franklin A. D., Afzali A., High purity isolation and quantification of semiconducting carbon nanotubes via column chromatography. ACS Nano 7, 2971–2976 (2013). [DOI] [PubMed] [Google Scholar]

- 17.Cao Q., Han S.-j., Tulevski G. S., Zhu Y., Lu D. D., Haensch W., Arrays of single-walled carbon nanotubes with full surface coverage for high-performance electronics. Nat. Nanotechnol. 8, 180–186 (2013). [DOI] [PubMed] [Google Scholar]

- 18.Wu J., Antaris A., Gong M., Dai H., Top-down patterning and self-assembly for regular arrays of semiconducting single-walled carbon nanotubes. Adv. Mater. 26, 6151–6156 (2014). [DOI] [PubMed] [Google Scholar]

- 19.Shulaker M. M., Pitner G., Hills G., Giachino M., Wong H. S. P., Mitra S., High-performance carbon nanotube field-effect transistors. IEEE Int. Electron Devices Meet. 33.6.1–33.6.4 (2014). [Google Scholar]

- 20.Hennrich F., Li W., Fischer R., Lebedkin S., Krupke R., Kappes M. M., Length-sorted, large-diameter, polyfluorene-wrapped semiconducting single-walled carbon nanotubes for high-density, short-channel transistors. ACS Nano 10, 1888–1895 (2016). [DOI] [PubMed] [Google Scholar]

- 21.Park S., Pitner G., Giri G., Koo J. H., Park J., Kim K., Wang H., Sinclair R., Wong H.-S. P., Bao Z., Large-area assembly of densely aligned single-walled carbon nanotubes using solution shearing and their application to field-effect transistors. Adv. Mater. 27, 2656–2662 (2015). [DOI] [PubMed] [Google Scholar]

- 22.Lefebvre J., Ding J., Li Z., Cheng F., Du N., Malenfant P. R. L., Hysteresis free carbon nanotube thin film transistors comprising hydrophobic dielectrics. Appl. Phys. Lett. 107, 243301 (2015). [Google Scholar]

- 23.Schießl S. P., Fröhlich N., Held M., Gannott F., Schweiger M., Forster M., Scherf U., Zaumseil J., Polymer-sorted semiconducting carbon nanotube networks for high-performance ambipolar field-effect transistors. ACS Appl. Mater. Interfaces 7, 682–689 (2015). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 24.Bisri S. Z., Derenskyi V., Gomulya W., Salazar-Rios J. M., Fritsch M., Fröhlich N., Jung S., Allard S., Scherf U., Loi M. A., Anomalous carrier transport in ambipolar field-effect transistor of large diameter single-walled carbon nanotube network. Adv. Electron. Mater. 2, 1500222 (2016). [Google Scholar]

- 25.Miyata Y., Shiozawa K., Asada Y., Ohno Y., Kitaura R., Mizutani T., Shinohara H., Length-sorted semiconducting carbon nanotubes for high-mobility thin film transistors. Nano Res. 4, 963–970 (2011). [Google Scholar]

- 26.Che Y., Badmaev A., Jooyaie A., Wu T., Zhang J., Wang C., Galatsis K., Enaya H. A., Zhou C., Self-aligned T-gate high-purity semiconducting carbon nanotube RF transistors operated in quasi-ballistic transport and quantum capacitance regime. ACS Nano 6, 6936–6943 (2012). [DOI] [PubMed] [Google Scholar]

- 27.Nougaret L., Happy H., Dambrine G., Derycke V., Bourgoin J.-P., Green A. A., Hersam M. C., 80 GHz field-effect transistors produced using high purity semiconducting single-walled carbon nanotubes. Appl. Phys. Lett. 94, 243505 (2009). [Google Scholar]

- 28.Cao Y., Che Y., Gui H., Cao X., Zhou C., Radio frequency transistors based on ultra-high purity semiconducting carbon nanotubes with superior extrinsic maximum oscillation frequency. Nano Res. 9, 363–371 (2016). [Google Scholar]

- 29.Cao Y., Brady G. J., Gui H., Rutherglen C., Arnold M. S., Zhou C., Radio frequency transistors using aligned semiconducting carbon nanotubes with current-gain cutoff frequency and maximum oscillation frequency simultaneously greater than 70 GHz. ACS Nano 10, 6782–6790 (2016). [DOI] [PubMed] [Google Scholar]

- 30.Joo Y., Brady G. J., Arnold M. S., Gopalan P., Dose-controlled, floating evaporative self-assembly and alignment of semiconducting carbon nanotubes from organic solvents. Langmuir 30, 3460–3466 (2014). [DOI] [PubMed] [Google Scholar]

- 31.Brady G. J., Joo Y., Wu M.-Y., Shea M. J., Gopalan P., Arnold M. S., Polyfluorene-sorted, carbon nanotube array field-effect transistors with increased current density and high on/off ratio. ACS Nano 8, 11614–11621 (2014). [DOI] [PubMed] [Google Scholar]

- 32.Brady G. J., Joo Y., Roy S. S., Gopalan P., Arnold M. S., High performance transistors via aligned polyfluorene-sorted carbon nanotubes. Appl. Phys. Lett. 104, 083107 (2014). [Google Scholar]

- 33.Mistry K. S., Larsen B. A., Blackburn J. L., High-yield dispersions of large-diameter semiconducting single-walled carbon nanotubes with tunable narrow chirality distributions. ACS Nano 7, 2231–2239 (2013). [DOI] [PubMed] [Google Scholar]

- 34.Nish A., Hwang J.-Y., Doig J., Nicholas R. J., Highly selective dispersion of single-walled carbon nanotubes using aromatic polymers. Nat. Nanotechnol. 2, 640–646 (2007). [DOI] [PubMed] [Google Scholar]

- 35.Lee H. W., Yoon Y., Park S., Oh J. H., Hong S., Liyanage L. S., Wang H., Morishita S., Patil N., Park Y. J., Park J. J., Spakowitz A., Galli G., Gygi F., Wong P. H.-S., Tok J. B.-H., Kim J. M., Bao Z., Selective dispersion of high purity semiconducting single-walled carbon nanotubes with regioregular poly(3-alkylthiophene)s. Nat. Commun. 2, 541 (2011). [DOI] [PubMed] [Google Scholar]

- 36.Wang H., Mei J., Liu P., Schmidt K., Jiménez-Osés G., Osuna S., Fang L., Tassone C. J., Zoombelt A. P., Sokolov A. N., Houk K. N., Toney M. F., Bao Z., Scalable and selective dispersion of semiconducting arc-discharge carbon nanotubes by dithiafulvalene/thiophene copolymers for thin film transistors. ACS Nano 7, 2659–2668 (2013). [DOI] [PubMed] [Google Scholar]

- 37.Ding J., Li Z., Lefebvre J., Cheng F., Dunford J. L., Malenfant P. R. L., Humes J., Kroeger J., A hybrid enrichment process combining conjugated polymer extraction and silica gel adsorption for high purity semiconducting single-walled carbon nanotubes (SWCNT). Nanoscale 7, 15741–15747 (2015). [DOI] [PubMed] [Google Scholar]

- 38.Tyler T. P., Brock R. E., Karmel H. J., Marks T. J., Hersam M. C., Electronically monodisperse single-walled carbon nanotube thin films as transparent conducting anodes in organic photovoltaic devices. Adv. Energy Mater. 1, 785–791 (2011). [Google Scholar]

- 39.Engel M., Small J. P., Steiner M., Freitag M., Green A. A., Hersam M. S., Avouris P., Thin film nanotube transistors based on self-assembled, aligned, semiconducting carbon nanotube arrays. ACS Nano 2, 2445–2452 (2008). [DOI] [PubMed] [Google Scholar]

- 40.Dowgiallo A.-M., Mistry K. S., Johnson J. C., Reid O. G., Blackburn J. L., Probing exciton diffusion and dissociation in single-walled carbon nanotube-C60 heterojunctions. J. Phys. Chem. Lett. 7, 1794–1799 (2016). [DOI] [PubMed] [Google Scholar]

- 41.Kane A. A., Ford A. C., Nissen A., Krafcik K. L., Léonard F., Etching of surfactant from solution-processed, type-separated carbon nanotubes and impact on device behavior. ACS Nano 8, 2477–2485 (2014). [DOI] [PubMed] [Google Scholar]

- 42.Radosavljević M., Heinze S., Tersoff J., Avouris P., Drain voltage scaling in carbon nanotube transistors. Appl. Phys. Lett. 83, 2435–2437 (2003). [Google Scholar]

- 43.Ghani T., Armstrong M., Auth C., Bost M., Charvat P., Glass G., Hoffmann T., Johnson K., Kenyon C., Klaus J., McIntyre B., Mistry K., Murthy A., Sandford J., Silberstein M., Sivakumar S., Smith P., Zawadzki K., Thompson S., Bohr M., A 90nm high volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors. IEEE Int. Electron Devices Meet. Tech. Dig., 11.6.1–11.6.3 (2003). [Google Scholar]

- 44.Shulaker M. M., Hills G., Patil N., Wei H., Chen H.-Y., Wong H.-S. P., Mitra S., Carbon nanotube computer. Nature 501, 526–530 (2013). [DOI] [PubMed] [Google Scholar]

- 45.Purewal M. S., Hong B. H., Ravi A., Chandra B., Hone J., Kim P., Scaling of resistance and electron mean free path of single-walled carbon nanotubes. Phys. Rev. Lett. 98, 186808 (2007). [DOI] [PubMed] [Google Scholar]

- 46.Chen Y.-F., Fuhrer M. S., Tuning from thermionic emission to ohmic tunnel contacts via doping in Schottky-barrier nanotube transistors. Nano Lett. 6, 2158–2162 (2006). [DOI] [PubMed] [Google Scholar]

- 47.Derycke V., Martel R., Appenzeller J., Avouris P., Controlling doping and carrier injection in carbon nanotube transistors. Appl. Phys. Lett. 80, 2773 (2002). [DOI] [PubMed] [Google Scholar]

- 48.Franklin A. D., Farmer D. B., Haensch W., Defining and overcoming the contact resistance challenge in scaled carbon nanotube transistors. ACS Nano 8, 7333–7339 (2014). [DOI] [PubMed] [Google Scholar]

- 49.Moonoosawmy K. R., Kruse P., To dope or not to dope: The effect of sonicating single-wall carbon nanotubes in common laboratory solvents on their electronic structure. J. Am. Chem. Soc. 130, 13417–13424 (2008). [DOI] [PubMed] [Google Scholar]

- 50.Wang H., Luo J., Robertson A., Ito Y., Yan W., Lang V., Zaka M., Schäffel F., Rümmeli M. H., Briggs G. A. D., Warner J. H., High-performance field effect transistors from solution processed carbon nanotubes. ACS Nano 4, 6659–6664 (2010). [DOI] [PubMed] [Google Scholar]

- 51.Avery A. D., Zhou B. H., Lee E.-S., Miller E. M., Ihly R., Wesenberg D., Mistry K. S., Guillot S. L., Zink B. L., Kim Y.-H., Blackburn J. L., Ferguson A. J., Tailored semiconducting carbon nanotube networks with enhanced thermoelectric properties. Nat. Energy 1, 16033 (2016). [Google Scholar]

- 52.Riesz P., Berdahl D., Christman C. L., Free-radical generation by ultrasound in aqueous and nonaqueous solutions. Environ. Health Perspect. 64, 233–252 (1985). [DOI] [PMC free article] [PubMed] [Google Scholar]

- 53.Zhao W., Cao T., White J. M., On the origin of green emission in polyfluorene polymers: The roles of thermal oxidation degradation and crosslinking. Adv. Funct. Mater. 14, 783–790 (2004). [Google Scholar]

- 54.Franklin A. D., Chen Z., Length scaling of carbon nanotube transistors. Nat. Nanotechnol. 5, 858–862 (2010). [DOI] [PubMed] [Google Scholar]

- 55.Choi S.-J., Bennett P., Takei K., Wang C., Lo C. C., Javey A., Bokor J., Short-channel transistors constructed with solution-processed carbon nanotubes. ACS Nano 7, 798–803 (2013). [DOI] [PubMed] [Google Scholar]

- 56.Solomon P. M., A comparison of semiconductor devices for high-speed logic. Proc. IEEE 70, 489–509 (1982). [Google Scholar]

- 57.Nguyen L. D., Tasker P. J., Radulescu D. C., Eastman L. F., Characterization of ultra-high-speed pseudomorphic AlGaAs/InGaAs (on GaAs) MODFETS. IEEE T. Electron Dev. 36, 2243–2248 (1989). [Google Scholar]

- 58.Schwierz F., Graphene transistors. Nat. Nanotechnol. 5, 487–496 (2010). [DOI] [PubMed] [Google Scholar]

- 59.Geier M. L., McMorrow J. J., Xu W., Zhu J., Kim C. H., Marks T. J., Hersam M. C., Solution-processed carbon nanotube thin-film complementary static random access memory. Nat. Nanotechnol. 10, 944–948 (2015). [DOI] [PubMed] [Google Scholar]

- 60.Qiu C., Zhang Z., Zhong D., Si J., Yang Y., Peng L.-M., Carbon nanotube feedback-gate field-effect transistor: Suppressing current leakage and increasing on/off ratio. ACS Nano 9, 969–977 (2015). [DOI] [PubMed] [Google Scholar]

- 61.Franklin A. D., Koswatta S. O., Farmer D. B., Smith J. T., Gignac L., Breslin C. M., Han S.-J., Tulevski G. S., Miyazoe H., Haensch W., Tersoff J., Carbon nanotube complementary wrap-gate transistors. Nano Lett. 13, 2490–2495 (2013). [DOI] [PubMed] [Google Scholar]

- 62.Cao Q., Xia M., Kocabas C., Shim M., Rogers J. A., Rotkin S. V., Gate capacitance coupling of singled-walled carbon nanotube thin-film transistors. Appl. Phys. Lett. 90, 023516 (2007). [Google Scholar]

- 63.Ghani T., Mistry K., Packan P., Thompson S., Stettler M., Tyagi S., Bohr M., Scaling challenges and device design requirements for high performance sub-50 nm gate length planar CMOS transistors. Symp. VLSI Technol. Dig. Tech. Pap., 174–175 (2000). [Google Scholar]

- 64.Lee J. S., Ryu S., Yoo K., Choi I. S., Yun W. S., Kim J., Origin of gate hysteresis in carbon nanotube field-effect transistors. J. Phys. Chem. C 111, 12504–12507 (2007). [Google Scholar]

- 65.Ha T.-J., Kiriya D., Chen K., Javey A., Highly stable hysteresis-free carbon nanotube thin-film transistors by fluorocarbon polymer encapsulation. ACS Appl. Mater. Interfaces 6, 8441–8446 (2014). [DOI] [PubMed] [Google Scholar]

- 66.Franklin A. D., Tulevski G. S., Han S.-J., Shahrjerdi D., Cao Q., Chen H.-Y., Wong H.-S. P., Haensch W., Variability in carbon nanotube transistors: Improving device-to-device consistency. ACS Nano 6, 1109–1115 (2012). [DOI] [PubMed] [Google Scholar]

- 67.Wahab M. A., Jin S. H., Islam A. E., Kim J., Kim J.-h., Yeo W.-H., Lee D. J., Chung H. U., Rogers J. A., Alam M. A., Electrostatic dimension of aligned-array carbon nanotube field-effect transistors. ACS Nano 7, 1299–1308 (2013). [DOI] [PubMed] [Google Scholar]

- 68.Cao Q., Han S.-J., Tulevski G. S., Franklin A. D., Haensch W., Evaluation of field-effect mobility and contact resistance of transistors that use solution-processed single-walled carbon nanotubes. ACS Nano 6, 6471–6477 (2012). [DOI] [PubMed] [Google Scholar]

- 69.Cao Q., Han S.-j., Penumatcha A. V., Frank M. M., Tulevski G. S., Tersoff J., Haensch W. E., Origins and characteristics of the threshold voltage variability of quasiballistic single-walled carbon nanotube field-effect transistors. ACS Nano 9, 1936–1944 (2015). [DOI] [PubMed] [Google Scholar]

- 70.Cao Q., Tersoff J., Han S.-J., Penumatcha A. V., Scaling of device variability and subthreshold swing in ballistic carbon nanotube transistors. Phys. Rev. Appl. 4, 024022 (2015). [Google Scholar]

- 71.Kim H., Colavita P. E., Paoprasert P., Gopalan P., Kuech T. F., Hamers R. J., Grafting of molecular layers to oxidized gallium nitride surfaces via phosphonic acid linkages. Surf. Sci. 602, 2382–2388 (2008). [Google Scholar]

- 72.Zhou X., Park J.-Y., Huang S., Liu J., McEuen P., Band structure, phonon scattering, and the performance limit of single-walled carbon nanotube transistors. Phys. Rev. Lett. 95, 146805 (2005). [DOI] [PubMed] [Google Scholar]

- 73.Weisman R. B., Bachilo S. M., Dependence of optical transition energies of structure for single-walled carbon nanotubes in aqueous suspension: An empirical Kataura plot. Nano Lett. 3, 1235–1238 (2003). [Google Scholar]

- 74.Ouyang Y., Guo J., Assessment of carbon nanotube array transistors: A three-dimensional quantum simulation. Solid State Electron. 61, 18–22 (2011). [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.

Supplementary Materials

Supplementary material for this article is available at http://advances.sciencemag.org/cgi/content/full/2/9/e1601240/DC1

Supplementary Text

fig. S1. Full sweep transfer characteristics.

fig. S2. Lead resistance subtraction.

fig. S3. Optical spectroscopy evidence of high semiconducting purity.

fig. S4. Effect of annealing on Ion/Ioff.

fig. S5. Ioff variability.

fig. S6. Postdeposition treatment effect on output characteristics.

fig. S7. Optical absorbance spectra used to verify XPS atomic concentrations and CNT diameter distribution.

fig. S8. Atomic force microscopy height measurement used to quantify packing density for XPS calibration.

fig. S9. Temperature-dependent FTIR measurement of PFO-BPy side chains and backbone.

fig. S10. On-conductance comparison of “annealed” versus “rinsed + annealed” treatments.

fig. S11. Conductance per tube measured for FETs with Lch < 150 nm.

fig. S12. Contact resistance and mean free path extraction.

table S1. Surface treatment XPS summary.

table S2. CNT FET performance comparisons.